15-JAN-2013 ==

meeting restart?

If

anyone wants to

call in:

(808) 956-2920

(single line,

first come, first

serve)

Agenda:

1 - AMBER (to be covered in the morning Amber meeting, I

think)

2 - ARA

A - assembly

(Travis/Brian/Brendan/Windell)

- pre-amps

........................ done

- downhole optical

zonus .... 2 assembled; others

to be assembled this week (Christian/Windell/Brian)

- receivers (FOAM)

............. 5 boxes ready

- power box

.......................

need to trim the 12V supply under

load; need to write email/elog about wiring scheme; need

to cold-test

- DAQ box

......................... Moxa,

Rb+clock+2 TTL boosts in place, deep antenna input chain

in place; wiring to do still (Brian/Windell/Brendan)

- power->DAQ box cable .... done

- 300V->power box cable ....

done

- 2 DAQ box power cables .. needed for testing

B - cold testing of complete

components

- pre-amps

......................... 17 done ... need to check if

the two removed LARK filters are in spec

- downhole

optical zonus .... 2 done over the weekend; awaiting assembly of

others

- receivers

(FOAM) ............. 3 boxes

done, 2 more to go

- power box

........................

- DAQ box

..........................

C - antennae (Peter/Christian/Brian)

D - shipping for deployment

[arrive at Pole by Dec 10] (everyone)

THURSDAY: pack preamps, downhole zonus, receivers, power

box, 300V power supply, test equipment

FRIDAY: ship to Pole

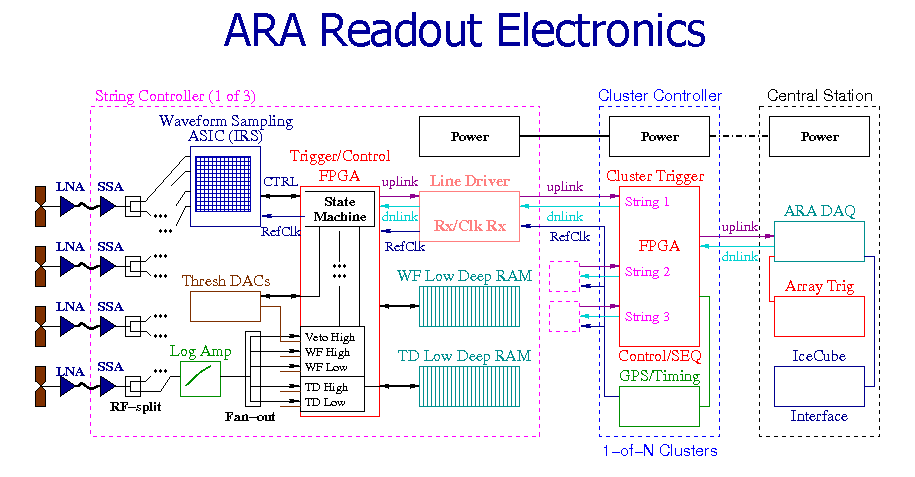

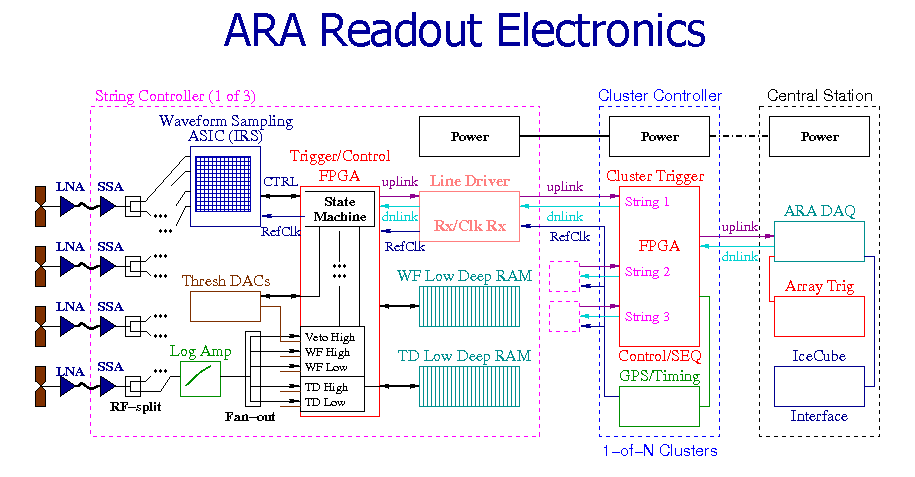

E - DAQ system

(Brendan/Windell/Ben/Luca)

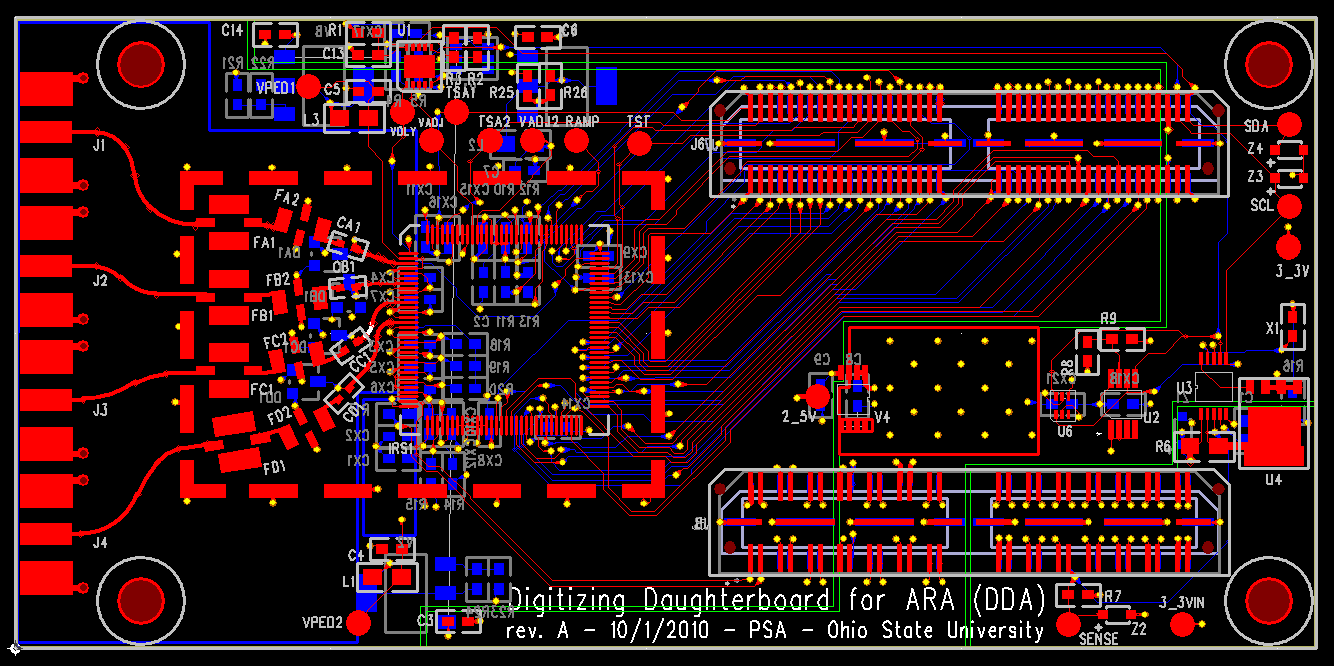

- DDA_EVAL

....................... working: can read/write to DDA

& read out a pedestal trigger from DDA

- surface TDA

status ............ need to test with surface preamps+receiver using

DDA_EVAL board

- AT-AT

temperature board .... cold-tested;

works as advertised

- ATRI

status/firmware

. ATRI board

.....................

x-ray Hawaii-01 (the one that

worked) and ATRI-09 (a new one from Sierra that does not

work) boards

- ICRR

status

. SBC ............................... ARA2

operating system runs, was able to load the FPGA

on the ICRR, and was able to read board id and

version registers

. ICRR board .....................

trigger: have checked the

diode trigger inputs (all good, see clean, +225

mV signals from VAM-6 for SNR ~10 input signals)

have switched batwing trigger

inputs to diode triggers; tested to see +225 mV

signals from VAM-6 for SNR ~10 input signals

signal: checked

all rf signal inputs - all now good; switched

capacitors on batwing channels 5-8 to lower

low-end of high-pass filter

FPGA: have switched batwing

(+/-) trigger to discone (+) only triggers

replaced trigger

algorithm with 5/12 deep & 3/4 surface; see waveforms in proper places for

surface and deep triggered events

need to fix the SMB

trigger so that it reads out the proper time

window when there's a trigger and does not break

the rf trigger time window

. calpulser interface ........... Diolan USB<->I2C (3.3V) translator

cold-tested with AT-AT temperature board; no

problems seen; need to discuss wiring

for I2C bus with Patrick

. GPS .............................. need a 3.3/5V -> 3V power

regulator - Windell purchased one

F -

calibration pulser

- control board .................... received boards back from

Patrick; need to test new pulser

- deep board .......................

instructions for testing from Kara; need to finish

power box & DAQ box and then test

- surface cal board .............. awaiting

arrival of a spare calpulser surface board for

working with deep board after power box goes to

Pole

G - cables

(Travis/Ben/Windell)

- LMR-610 .......................... ELOG

done with S12 & TDR measurements (shipped to

Pole)

- 6m Helix .......................... S12

& TDR measurements done, data needs to put on

ELOG (shipped to Pole)

- downhole fiber

.................. S12 & Power

measurements done - one poor fiber, all else okay

H - surface

antenna integration (Peter/Travis/Brendan/Luca)

. Preamps

..................................... tested warm

(noise meter & network analyzer; setting

filter window) - will need to be lock-tighted,

etc. later

.

Receiver box ...............................

tested warm (with pulser pulser)

.

Power detectors ..........................

tested; redoing wiring (switch to Teflon/twist

pairs) as prep for placement in DAQ box

.

V0 Surface TDA .......................... can

set DACs; card is probably not useable:

threshold to close to edge of card; also

surface combinatoric trigger signal not seen

with pulser so firmware needs a fix

. V1 Surface TDA

.......................... testing on DDA_EVAL

3 - ANITA3 hardware development (main

meeting: moved to Wednesdays)

A - Firmware Update

(Lisa)

1. Xilinx eval

board Implementation check status? (w/Luca)

B - ASICs updates (Gary)

1. LAB4 are in hand (eval board - Gary

start - Zhe finish?)

2. RITC

are in hand (eval board - Kurtis start - Zhe

finish?)

3. ARM

silicon compilation check IBM 130nm (Lisa/Luca)

C - SURF/TURF plans (Zhe Cao

arrived)

4 - EVA placeholder

5 - All other business

22-NOV-2011

13:30 -- note unusual time (local

Radio meeting):

1 - AMBER update

[pdf]

(Rishi & Patrick in Argentina/Roberto?)

2 - ARA

A - testing the pieces in the

Freezer (Brendan/Ben)

- LARK notched

filters ......... 21 tested and good

- LARK not-notched

filters ... 19 (maybe 20) tested

- optical zonus

................... 15 good cold tested, 1 warm

tested good, 1 of 16 good ones found bad when

retested on many Sundays ago

- ATRI board

......................

B - assembly

(Travis/Brian/Brendan/Windell)

- pre-amps

........................ done

- downhole optical

zonus .... 1 assembled; others

to be assembled this week (Christian)

- receivers (FOAM)

............ 4 boxes ready

& 1 awaiting 5dB attenuator

- power box

.......................

all power

supplies in place; warm-tested; need to finish wiring the

calibration pulser control lines

- DAQ box

......................... supports

for Moxa, Rb+clock+2 TTL boosts in place, 1/2 deep

antenna input chain in place; wiring to do still

(Brian/Windell/Brendan)

- power->DAQ box cable .... done

- 300V->power box cable ....

done

C - cold testing of complete components

- pre-amps

......................... done ... need to check if the

two removed LARK filters are in spec

- downhole optical

zonus ....

- receivers (FOAM)

............. 3 boxes, 2 more to

go

- power box

........................

- DAQ box

.........................

D - DAQ system (Brendan/Windell/Ben/Luca)

- DDA_EVAL

....................... working: can read/write to DDA

& read out a pedestal trigger from DDA

- DDA status

....................... need

to replace WF2 connectors with WF connects; need

to clean Samtec connectors; need to return bad LS bit DDA' to

Patrick

- TDA status

....................... all four channels work; see

expected gain

TO DO: - need to

replace power overload sense resistors

- have threshold curves for 3 out of 4

TDAs using 5 dB attenuators; need to do threshold curves for

1 TDAs; need to decide upon input attenuation

- surface TDA

status ........... ARAacqd software now able to control

DAC & do threshold scans

- temperature board

............. received from Patrick, will be tested

after being integrated into DAQ box

- ATRI status/firmware

. SBC

............................... OSU one crashes rather often too

locks up rather

more often than not, usually during a read to the

flash card

. ATRI board

..................... FX2

(Cypress) chip death - replaced FX2 on Hawaii-01

board, SBC still does not see the FX2

replaced transistor fix (since I burned it out), but

oscillator now dead

. FPGA

............................. continuing

to debug the event readout

-

self-triggered data exhibits one time-bin spikes and

dips when trigger rate rises above ~2 to 20 Hz (CAUSE:

blocking IRS readout for order ms)

- trigger readout is limited to 2Hz for some

as-yet-unknown reason (CAUSE: threading issue in

ARAAcqd)

- low 'first block' in event data (CAUSE: transitions

in signals)

- odd fluctations around block 20 in event data

(CAUSE: pick up from too many simultaneous

transitions)

STILL OPEN:

- addition of a

'reset' method to firmware for clean start up of

FPGA+FX2

- test

updated FX2 firmware from Jonathan - second

update to be tested

- started integrating &

testing surface trigger: v0 card doesn't meet our

needs; v1 card arrived from Uwe; combinatoric

trigger not seen in Chipscope

. ARAAcqd

...................... update

needed for proper surface trigger threshold

scan

.

calibration data-taking ..... Vadj

scan done, but other data will not be collected

before DAQ assembly due to ATRI board death

- ICRR status

. SBC

............................... ARA2 operating system runs, was

able to load the FPGA on the ICRR, and was able

to read board id and version registers

. ICRR board

..................... trigger: checked the diode trigger inputs

(all good, see clean, +225 mV signals from VAM-6

for SNR ~10 input signals)

switched

batwing trigger inputs to diode triggers; tested

to see +225 mV signals from VAM-6 for SNR ~10

input signals

signal: checked all rf signal inputs -

all now good; switched capacitors on batwing

channels 5-8 to lower low-end of high-pass

filter

FPGA: switched batwing (+/-) trigger

to discone (+) only triggers

replaced trigger algorithm with 5/12 deep

& 3/4 surface; need

to test surface part of this trigger

need

to fix the SMB trigger so that it reads out the

proper time window when there's a trigger and

does not break the rf trigger time window

. calpulser

interface ........... talking

with Ryan, Jonathan, and Patrick about a

USB<->I2C (3.3V) converter

. GPS

.............................. need 3.3/5V -> 3V power

regulator

E - calibration pulser

- control board

.................... received

boards back from Patrick, need to test new

pulser

- deep board

....................... instructions for testing

from Kara, need to finish power box & DAQ box

and then test

F - cables (Travis/Ben/Windell)

- LMR-610

.......................... ELOG done with S12

& TDR measurements (shipped to Pole)

- 6m Helix

.......................... S12 & TDR

measurements done, data needs to put on ELOG

(shipped to Pole)

- downhole fiber

.................. S12 & Power

measurements done - one poor fiber, all else okay

G - surface antenna integration

(Peter/Travis/Brendan/Luca)

.

Preamps .....................................

tested warm (noise meter & network analyzer;

setting filter window) - will need to be

lock-tighted, etc. later

.

Receiver box ...............................

tested warm (with pulser pulser)

.

Power detectors ..........................

tested; redoing wiring (switch to Teflon/twist

pairs) as prep for placement in DAQ box

.

V0 Surface TDA .......................... can

set DACs; card is probably not useable:

threshold to close to edge of card; also

surface combinatoric trigger signal not seen

with pulser so firmware needs a fix

. V1 Surface TDA

.......................... testing on DDA_EVAL

H - antennae (Peter/Christian/Brian)

I - shipping

3 - ANITA3 hardware development (main

meeting: moved to Wednesdays)

A - Firmware Update

(Lisa)

1. Xilinx eval

board Implementation check status? (w/Luca)

B - ASICs updates (Gary)

1. LAB4 are in hand (eval board - Gary

start - Zhe finish?)

2. RITC

are in hand (eval board - Kurtis start - Zhe

finish?)

3. ARM

silicon compilation check IBM 130nm (Lisa/Luca)

C - SURF/TURF

plans

4 - EVA placeholder

5 - All other business

7-NOV-2011 11am? (local Radio

meeting):

Due to faculty candidate Special

Colloquium at 3:30pm this afternoon,

we'll hold the weekly meeting after

the ANITA phone call ends ... if

anyone

wants to call in, the phone number is:

(808)

956-2920

Note

that this

phone is only

one line, so

it is

availability

is first

come/first

served.

Agenda:

1 - AMBER (Rishi in Argentina/Roberto)

[PDF]

- LARK notched filters

......... 21 tested and good

- optical zonus

................... 15 good cold tested, 1 warm tested

good, 1 of 16 good ones found bad

when retested on Sunday

- downhole optical

zonus .... ready for assembly

(Brian/Christian/Travis)