|

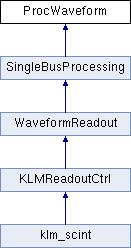

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_MISC | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| baseline_g | std_logic_vector ( 11 downto 0 ) |

| WAVE_MEM_DEPTH | integer := 4 |

| B2TT_RST_PPLN_STGS | integer := 5 |

| STAT_REG_PPLN_STGS | integer := 5 |

| FIFO_RST_PPLN_STGS | integer := 6 |

| SPSBlockRAM_READ_LATENCY | integer := 6 |

| N_BITS_AVG_g | integer |

Ports | |

| clk | in std_logic := ' 0 ' |

| rst | in std_logic := ' 0 ' |

| ena | in std_logic := ' 0 ' |

| ped_sub_ena | in std_logic |

| control registers | |

| measure_peds | in std_logic |

| stream_peds | in std_logic |

| N_readout_samples | in std_logic_vector ( 7 downto 0 ) |

| LE_time_thresh | in std_logic_vector ( 11 downto 0 ) := " 000000110010 " |

| busy | out std_logic := ' 0 ' |

| status registers | |

| debug_we | out std_logic := ' 0 ' |

| debug_wave | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| win_samp_start | in slv14 ( 4 downto 0 ) := ( others = > ( others = > ' 0 ' ) ) |

| event info | |

| ch_mask | in slv15 ( 4 downto 0 ) := ( others = > " 000000000000000 " ) |

| fifo_rst | out std_logic := ' 0 ' |

| fifo access | |

| fifo_asic_sel | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_chan_sel | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_rd_ena | out std_logic := ' 0 ' |

| fifo_dout | in std_logic_vector ( 23 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_drdy | in std_logic := ' 0 ' |

| fifos_empty | in std_logic := ' 0 ' |

| rx_features_ack | in std_logic := ' 0 ' |

| wires to HitDataSerializer | |

| rx_features_ena | out std_logic := ' 0 ' |

| last_hit | out std_logic := ' 0 ' |

| peak | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| le_time | out std_logic_vector ( 13 downto 0 ) := ( others = > ' 0 ' ) |

| daq_chan | out std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| avg_peds_ena | in std_logic := ' 0 ' |

| wires needed for pedestal measurement | |

| avg_peds_busy | out std_logic := ' 0 ' |

| wr_peds2sram_ena | out std_logic := ' 0 ' |

| wr_peds2sram_ack | in std_logic := ' 0 ' |

| even_ped | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| odd_ped | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| sram_asic_addr | out std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| sram_chan_addr | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| sram_samp_addr | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| fe_dbg | out std_logic_vector ( 1 downto 0 ) := " 00 " |

| sps_reset | in std_logic := ' 0 ' |

| signals for measuring single-photon spectra | |

| SPS_hist_rd_addr | in std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) |

| SPS_hist_rd_data | out std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| Engineer | Create Date |

|---|---|

| Chris Ketter | 09/18/2019 |

The main state machine is enabled by the digNshift_done signal. A local copy of the finalized channel mask is used to determine when all waveforms have been processes.

Threre are 5 FSMs in this module. The first, and main one, is Extract_Features, which streams waveforms from the storage FIFOs, subtracts pedestals, finds charge and time, and initiates the next three FSMs. wr_debug_wave dumps all info into debug FIFOs located in KLMScrodRegCtrl. tx_features sends hit data to the hit_bldr FSM in WaveformReadout. fill_SPS makes a histogram of charge using block RAM for the purpose of offline SiPM gain calibration. The last FSM, avg_and_wr_peds, is only used for pedestal measurement.

Definition at line 32 of file ProcWaveform.vhd.