|

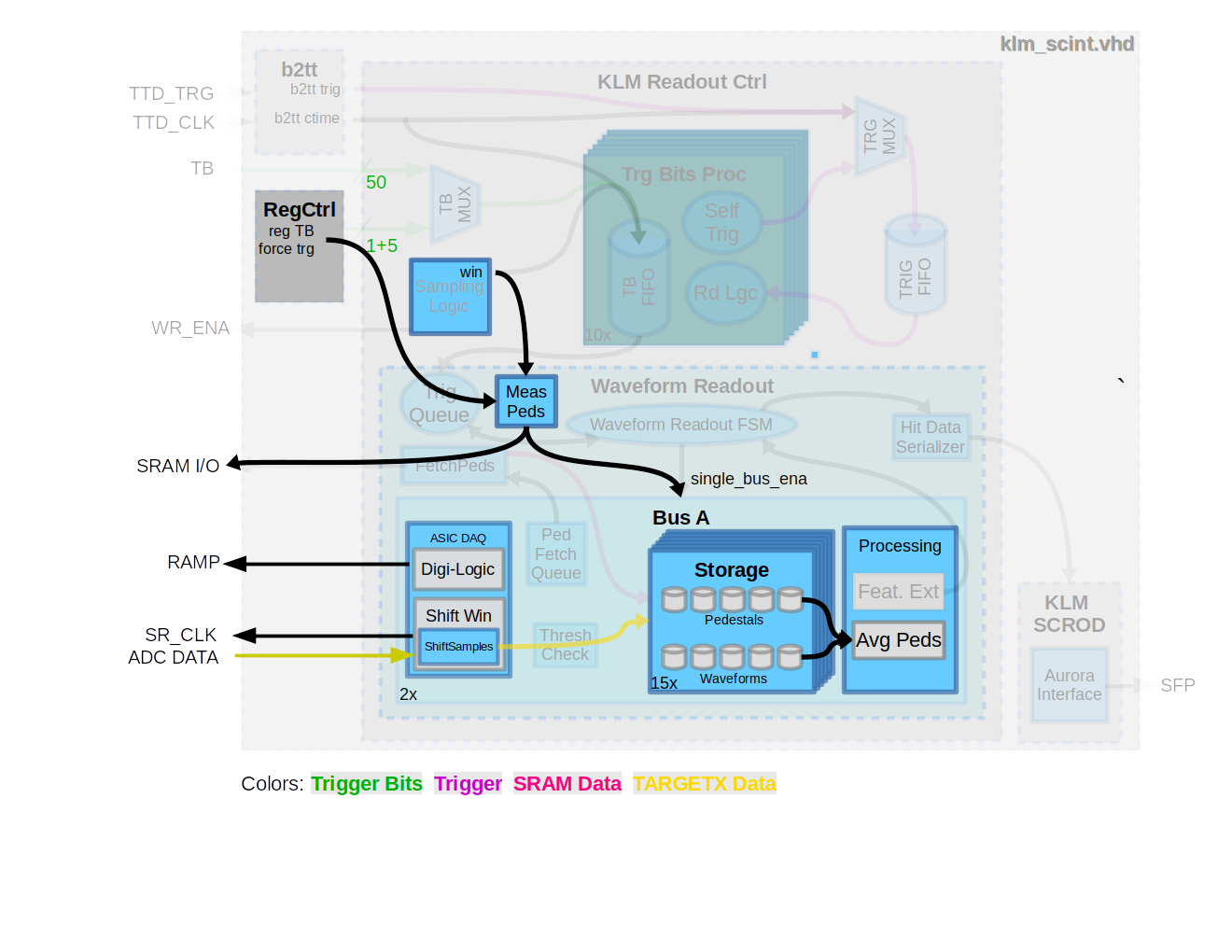

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_MISC | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| LAST_WINDOW_ADDRESS | std_logic_vector ( 8 downto 0 ) := " 111111111 " |

| N_BITS_AVG_g | integer |

| ANALOG_STORE_TIME | std_logic_vector ( 8 downto 0 ) := " 000001000 " |

Ports | |

| clk | in STD_logic |

| ena | in std_logic := ' 0 ' |

| busy | out std_logic := ' 0 ' |

| force_trig | out std_logic := ' 0 ' |

| trig_win | out std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| prime_fifos | out std_logic := ' 0 ' |

| summing_ena | out std_logic := ' 0 ' |

| cur_win | in std_logic_vector ( 8 downto 0 ) |

| either_bus_busy | in std_logic := ' 0 ' |

| avg_peds_ena | out std_logic := ' 0 ' |

| avg_peds_busy | in std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

| dig_busy | in std_logic |

The goal is to find the average of each pedestal and write it to off-FPGA memory. Pedestals are measured and added up 2^N times, then then shifted right N times (i.e. divided by 2^N) and written to memory.

MeasurePeds.vhd puts WaveAndPedStaging.vhd's fifos into summing mode, then triggers the readout 2^N times. Next, it tells ProcWaveform.vhd to take over. ProcWaveform.vhd reads and averages (i.e. bit shifts) the FIFOs, then interfaces with PedestalWriter.vhd's A/B-bus arbiter, ultimately writing the averaged pedestal values to external RAM. Finally, this module increments window number and repeats the process until all 512 windows have been measured.

Definition at line 30 of file MeasurePeds.vhd.