|

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_MISC | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Ports | |

| clk | in std_logic := ' 0 ' |

| rst | in std_logic := ' 0 ' |

| ena | in std_logic := ' 0 ' |

| busy | out std_logic := ' 0 ' |

| win_samp_start_asic | in slv14 ( 4 downto 0 ) := ( others = > ( others = > ' 0 ' ) ) |

| asic_mask | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| first_dig_win | in std_logic_vector ( 8 downto 0 ) |

| last_dig_win | in std_logic_vector ( 8 downto 0 ) |

| sample_data | out slv12 ( 14 downto 0 ) := ( others = > " 000000000000 " ) |

| samples_valid | out std_logic := ' 0 ' |

| current_asic | out std_logic_vector ( 4 downto 0 ) := " 00001 " |

| ramp_length | in std_logic_vector ( 11 downto 6 ) |

| t_samp_addr_settle | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| t_setup_ss_any | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| t_strobe_settle | in std_logic_vector ( 3 downto 0 ) := " 0100 " |

| t_sr_clk_high | in std_logic_vector ( 3 downto 0 ) := " 0010 " |

| t_sr_clk_low | in std_logic_vector ( 3 downto 0 ) := " 0010 " |

| t_sr_clk_strobe | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| N_readout_samples | in std_logic_vector ( 7 downto 0 ) |

| DigBusy | out std_logic := ' 0 ' |

| ShiftOutWinBusy | out std_logic := ' 0 ' |

| ShiftOutSampBusy | out std_logic := ' 0 ' |

| BUS_RD_ENA | out std_logic := ' 0 ' |

| BUS_CLR | out std_logic := ' 0 ' |

| BUS_RAMP | out std_logic := ' 0 ' |

| BUS_RD_WINSEL | out std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| BUS_DO | in std_logic_vector ( 14 downto 0 ) := ( others = > ' 0 ' ) |

| SR_CLR | out std_logic := ' 0 ' |

| SR_CLK | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| SR_SEL | out std_logic := ' 0 ' |

| SAMPLESEL | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| SAMPLESEL_ANY | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

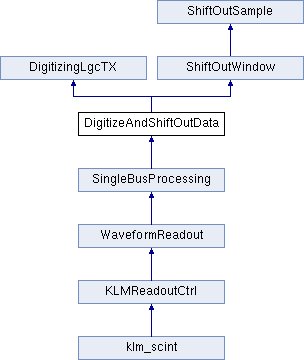

Digitize and Shift out all samples in ROI

Chris Ketter. 09/18/2019.

One window at a time, this module will digitize the window if it overlaps with the ROI, then, one sample at a time, it will shift out the sample if it's contained in the ROI. All ASICs and channels are digitized in parallel. Channels are shifted out in parallel, but asics are shifted out serially. Only ASICs specified in i_asic_mask are shifted out. Each time a single sample has been shifted out, samples_valid goes high so that the sample can be received by ThresholdCheck.vhd and written into the appropriate processing FIFO < >

Definition at line 27 of file DigitizeAndShiftOutData.vhd.