|

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| num_bits_wilk_adc | integer := 12 |

Ports | |

| clk | in std_logic := ' 0 ' |

| ena | in std_logic := ' 0 ' |

| busy | out std_logic := ' 0 ' |

| t_samp_addr_settle | in std_logic_vector ( 3 downto 0 ) := " 0100 " |

| t_sr_clk_strobe | in std_logic_vector ( 3 downto 0 ) := " 0000 " |

| t_strobe_settle | in std_logic_vector ( 3 downto 0 ) := " 0000 " |

| t_setup_ss_any | in std_logic_vector ( 3 downto 0 ) := " 0001 " |

| t_sr_clk_high | in std_logic_vector ( 3 downto 0 ) := " 0010 " |

| t_sr_clk_low | in std_logic_vector ( 3 downto 0 ) := " 0001 " |

| sr_asic_sel | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| samples_valid | out std_logic := ' 0 ' |

| sample_data | out slv12 ( 14 downto 0 ) := ( others = > " 000000000000 " ) |

| BUS_DO | in std_logic_vector ( 14 downto 0 ) := ( others = > ' 0 ' ) |

| SR_CLR | out std_logic := ' 0 ' |

| SR_CLK | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| SR_SEL | out std_logic := ' 0 ' |

| SAMPLESEL_ANY | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

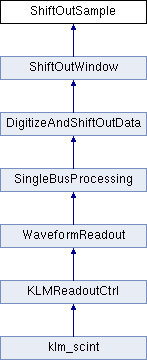

Asserts shift-register signals with tunable wait times for each step of the shift-out process.

After shifting out all 12 bits, a samples_ready flag is asserted and the samples are picked up by ThresholdCheck.vhd

Addressing of the sample via SAMPELSEL is taken care of one level up in ShiftOutWindow.vhd

SR_SEL __/‾‾‾\_________________________________________________________________ samplesel_any __/‾‾‾\_/1‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾\______ sr_clock ___/‾\_____/2‾\_/3‾\_/4‾\_/5‾\_/6‾\_/7‾\_/8‾\_/9‾\_/10\_/11\_/12\_______ BUS_DO ============1====2====3====4====5====6====7====8====9====10===11===12===

*For loading the test pattern, samplesel_any is held low while SR_SEL is high.

Definition at line 28 of file ShiftOutSample.vhd.