|

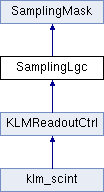

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| numeric_std | |

| vcomponents | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Ports | |

| clk | in std_logic |

| reset | in std_logic := ' 0 ' |

| ana_wr_ena_mask | in TARGETX_analong_wr_ena_mask_t |

| cur_win | out std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| BUSA_WR_ADDRCLR | out std_logic := ' 0 ' |

| BUSB_WR_ADDRCLR | out std_logic := ' 0 ' |

| WR1_ENA | out std_logic_vector ( 9 downto 0 ) := ( others = > ' 1 ' ) |

| WR2_ENA | out std_logic_vector ( 9 downto 0 ) := ( others = > ' 1 ' ) |

| SSTIN_N | out std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) |

| SSTIN_p | out std_logic_vector ( 9 downto 0 ) := ( others = > ' 1 ' ) |

2018/12/23 Original module from Isar 2018/12/24 Minor refactoring 2019/10/08 Remove unused signals, made simpler Outdated explanation:

Theory of operation for TargetX (IM:9/5/2014): clk period is 16 ns. clk/2 length is 8 ns SSTIN is always present with a 64 ns period: clk: 10101010 10101010 each bit is 8 ns SSTIN: 11110000 11110000 main counter++: 01000100 01000100 (as per TX simulations) main counter++: 00100010 00100010 (as per this implementation) when start is asseted, main counter is reset and SAMPLING starts by enabling wr1_ena and wr_2 ena. main counter is increased on either edge of SSTIN

Definition at line 33 of file SamplingLgc.vhd.