|

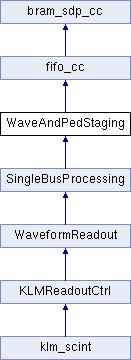

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| std_logic_1164 | |

| NUMERIC_STD | |

| std_logic_MISC | |

| std_logic_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| FIFO_DIN_SHIFT_DEPTH_g | integer := 2 |

Ports | |

| clk | in std_logic := ' 0 ' |

| reset | in std_logic := ' 0 ' |

| prime_fifos | in std_logic := ' 0 ' |

| summing_ena | in std_logic := ' 0 ' |

| wave_fifo_wr_asic | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| wave_fifo_wr_ena | in std_logic := ' 0 ' |

| main_samp_in | in std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_wr_asic | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_wr_ena | in std_logic := ' 0 ' |

| ped_fifo_din | in std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_rd_asic | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_rd_ena | in std_logic := ' 0 ' |

| fifo_dout | out std_logic_vector ( 23 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_drdy | out std_logic := ' 0 ' |

| fifos_empty | out std_logic := ' 0 ' |

Temporary waveform and pedestal memory for one channel on each of 5 asics. Because only one asic is read at a time, all fifo data i/o's are tied together while the enable signals are multiplexed based on asic number. This module will be instantiated 15 times per bus (2 buses)

In pedestal calculating mode, writing waveform samples to the wave fifo kicks off a state machine which first reads the wave and ped fifos, then adds the new sample to the sum of all prior iterations, and it stores this sum as a 24 bit vector shared by the wave and ped fifos. This scheme allows 2^12 averages of each pedestal value, but in practice 2^6 or 2^7 averages is sufficient.

Definition at line 24 of file WaveAndPedStaging.vhd.