|

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_MISC | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| baseline_g | std_logic_vector ( 11 downto 0 ) := " 110000000000 " |

| SLOW_CTRL_BUFF | integer := 5 |

| N_BITS_AVG_g | integer |

Ports | |

| clk | in std_logic := ' 0 ' |

| rst | in std_logic := ' 0 ' |

| ped_sub_ena | in std_logic |

| disambig_tb5 | in std_logic |

| measure_peds | in std_logic |

| stream_peds | in std_logic |

| ena | in std_logic := ' 0 ' |

| win_samp_start | in slv14 ( 4 downto 0 ) := ( others = > ( others = > ' 0 ' ) ) |

| trig_bits | in slv5 ( 4 downto 0 ) := ( others = > " 00000 " ) |

| asic_mask | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| first_dig_win | in std_logic_vector ( 8 downto 0 ) |

| last_dig_win | in std_logic_vector ( 8 downto 0 ) |

| ped_fetch_asic_no | out std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fetch_chan | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| ped_win_samp_start | out std_logic_vector ( 13 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fetch_ena | out std_logic := ' 0 ' |

| ped_fetch_ack | in std_logic := ' 0 ' |

| ped_fifo_wr_asic | in std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_wr_chan | in std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_wr_ena | in std_logic := ' 0 ' |

| ped_fifo_din | in std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| BUS_RD_ENA | out std_logic := ' 0 ' |

| BUS_RAMP | out std_logic := ' 0 ' |

| BUS_CLR | out std_logic := ' 0 ' |

| BUS_DO | in std_logic_vector ( 14 downto 0 ) := ( others = > ' 0 ' ) |

| SR_CLR | out std_logic := ' 0 ' |

| SR_CLK | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| SR_SEL | out std_logic := ' 0 ' |

| BUS_RD_WINSEL | out std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| SAMPLESEL | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| SAMPLESEL_ANY | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| rx_features_ack | in std_logic := ' 0 ' |

| rx_features_ena | out std_logic := ' 0 ' |

| last_hit | out std_logic := ' 0 ' |

| peak | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| le_time | out std_logic_vector ( 13 downto 0 ) := ( others = > ' 0 ' ) |

| daq_chan | out std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| ramp_length | in std_logic_vector ( 11 downto 6 ) |

| t_samp_addr_settle | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| t_setup_ss_any | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| t_strobe_settle | in std_logic_vector ( 3 downto 0 ) := " 0100 " |

| t_sr_clk_high | in std_logic_vector ( 3 downto 0 ) := " 0010 " |

| t_sr_clk_low | in std_logic_vector ( 3 downto 0 ) := " 0010 " |

| t_sr_clk_strobe | in std_logic_vector ( 3 downto 0 ) := " 0110 " |

| N_readout_samples | in std_logic_vector ( 7 downto 0 ) |

| LE_time_thresh | in std_logic_vector ( 11 downto 0 ) := " 110100010110 " |

| debug_we | out std_logic := ' 0 ' |

| debug_wave | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| DigStoreProcBusy | out std_logic := ' 0 ' |

| DigNShiftBusy | out std_logic := ' 0 ' |

| DigBusy | out std_logic := ' 0 ' |

| ShiftOutWinBusy | out std_logic := ' 0 ' |

| ShiftOutSampBusy | out std_logic := ' 0 ' |

| FeatExtBusy | out std_logic := ' 0 ' |

| PedFetchQueueBusy | out std_logic := ' 0 ' |

| prime_fifos | in std_logic := ' 0 ' |

| summing_ena | in std_logic := ' 0 ' |

| avg_peds_ena | in std_logic := ' 0 ' |

| avg_peds_busy | out std_logic := ' 0 ' |

| wr_peds2sram_ena | out std_logic := ' 0 ' |

| wr_peds2sram_ack | in std_logic := ' 0 ' |

| even_ped | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| odd_ped | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| sram_asic_addr | out std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| sram_chan_addr | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| sram_samp_addr | out std_logic_vector ( 4 downto 1 ) := ( others = > ' 0 ' ) |

| fe_dbg | out std_logic_vector ( 1 downto 0 ) := " 00 " |

| sps_reset | in std_logic := ' 0 ' |

| SPS_hist_rd_addr | in std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) |

| SPS_hist_rd_data | out std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

Digitize and process event on common motherboard bus (5 ASICs per bus)

| Engineer | Create Date |

|---|---|

| Chris Ketter | 07/18/2019 |

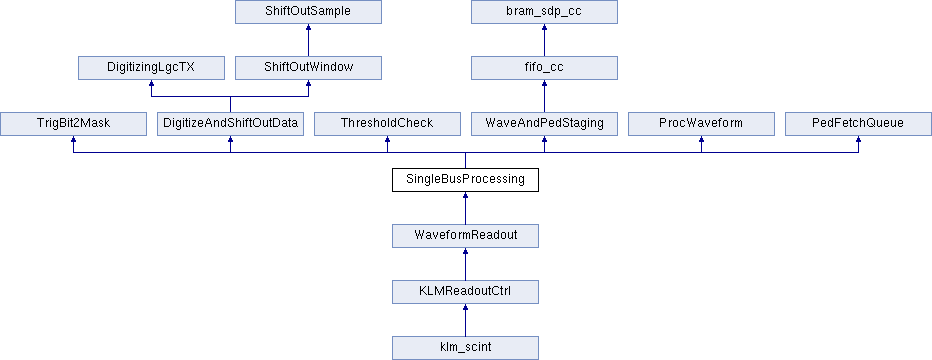

The SingleBusProcessing module is a container for all of the modules needed to digitize and process waveforms for 5 asics which are all on a common bus

A simple state machine below initiates the digitization process and waits for it to finish.

Definition at line 22 of file SingleBusProcessing.vhd.