|

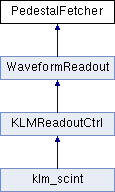

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| STD_LOGIC_1164 | |

| NUMERIC_STD | |

| STD_LOGIC_MISC | |

| STD_LOGIC_UNSIGNED | |

| klm_scint_pkg | Package <klm_scint_pkg> |

Generics | |

| ped_ram_tAA | integer range 0 to 15 := 9 |

Ports | |

| clk | in STD_logic |

| rst | in STD_logic |

| ena | in std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

| ack | out std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

| asic_addr | in slv3 ( 1 downto 0 ) |

| chan_addr | in slv4 ( 1 downto 0 ) := ( others = > " 0000 " ) |

| win_samp_start | in slv14 ( 1 downto 0 ) := ( others = > ( others = > ' 0 ' ) ) |

| fifo_asic_sel | out std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| fifo_chan_sel | out std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_wr_ena | out std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

| ped_fifo_din | out std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| N_readout_samples | in std_logic_vector ( 7 downto 0 ) |

| RAM_do | in std_logic_vector ( 7 downto 0 ) |

| RAM_ADDR | out std_logic_vector ( 21 downto 0 ) := ( others = > ' 1 ' ) |

Part: CY62177EV30

Access the pedestal ram and read values for region of intereset. The scope of this module is a single channel. This module should be enabled once for each channel in an event. The output data will be wired to the appropriate pedestal fifo in the parallel processing section. Input is an enable signal, starting hardware address, and number of samples to be fetched. To service both busses, these inputs are in parallel and an unbiased arbiter decides which bus to service first. There is also logic for making sure window rollover is handled appropriately.

| BUS | ASIC | CH | WIN | SAMP |

|---|---|---|---|---|

| 1 | 3 | 4 | 9 | 5 |

4M addresses available. 10 ASIC * 16 CH * 512 WIN * 32 SA * 1.5 bytes/SA = 3,932,160 bytes This requires storing 2 peds across 3 addresses, and converting (BUS & ASIC) to TXDC

/| TXDC | CH | WIN | SAMP[4:1] |\ ||----4----|----4----|-----------9------------|------4----|| * 3 + (0|1|2) \|---------|---------|------------------------|-----------|/

Data available at min T_aa = 55ns after address transition

clk \__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾\__/‾‾

RAM_do _‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_╳_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾

RAM_addr _‾_╳_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_‾_╳_‾_‾_‾_‾_‾_‾_‾

|<--------- T_aa ------------------------------>|<--- T_aa-----*Device continuously selected. RAM_rw=1, RAM_OEb=1

Definition at line 50 of file PedestalFetcher.vhd.