|

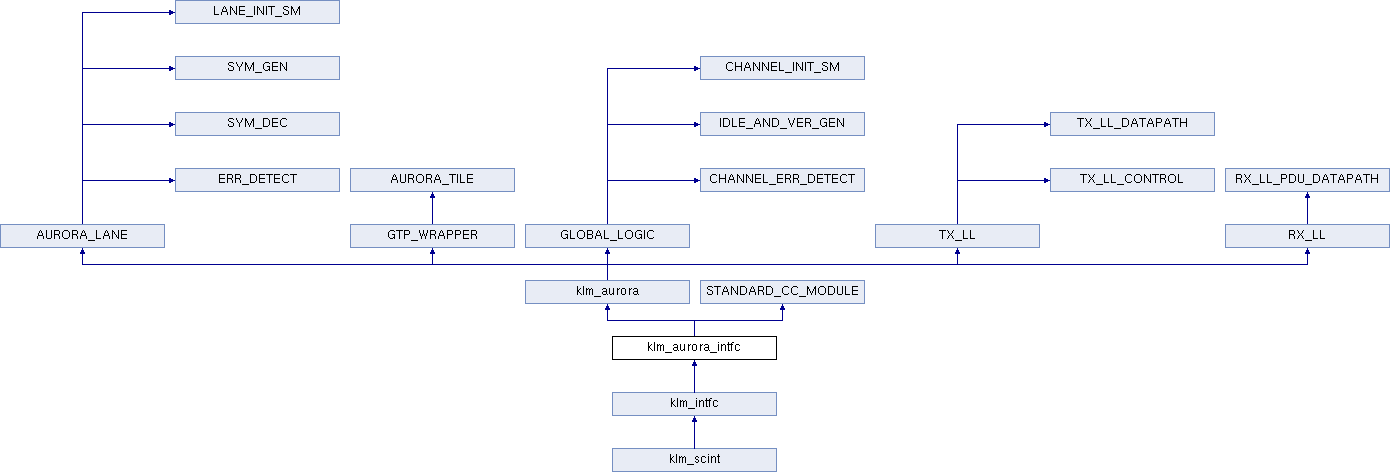

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

Entities | |

| MAPPED | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_misc | |

| aurora_pkg | |

Generics | |

| SIM_GTPRESET_SPEEDUP | integer := 1 |

| CLK_CORRECT_USE | boolean := TRUE |

Ports | |

| refseldypll | std_logic_vector ( 2 downto 0 ) |

| ref_clk0 | in std_logic |

| ref_clk1 | in std_logic |

| user_clk | in std_logic |

| sync_clk | in std_logic |

| reset | in std_logic |

| gt_reset | in std_logic |

| plllock | in std_logic |

| tx_dst_rdy_n | out std_logic |

| tx_src_rdy_n | in std_logic |

| tx_sof_n | in std_logic |

| tx_eof_n | in std_logic |

| tx_d | in std_logic_vector ( 0 to 15 ) |

| tx_rem | in std_logic |

| rx_src_rdy_n | out std_logic |

| rx_sof_n | out std_logic |

| rx_eof_n | out std_logic |

| rx_rem | out std_logic |

| rx_d | out std_logic_vector ( 0 to 15 ) |

| gtlock | out std_logic |

| hard_err | out std_logic |

| soft_err | out std_logic |

| frame_err | out std_logic |

| channel_up | out std_logic |

| lane_up | out std_logic |

| warn_cc | out std_logic |

| do_cc | out std_logic |

| powerdown | in std_logic |

| loopback | in std_logic_vector ( 2 downto 0 ) |

| rxp | in std_logic |

| rxn | in std_logic |

| txp | out std_logic |

| txn | out std_logic |

Definition at line 23 of file klm_aurora_intfc.vhd.