|

Belle II KLM Scint Firmware

1

|

|

Belle II KLM Scint Firmware

1

|

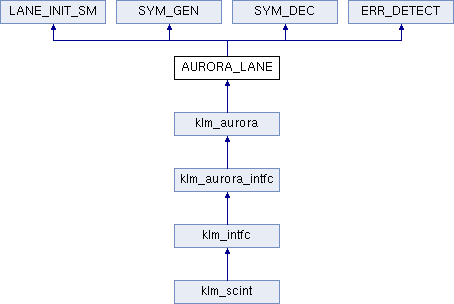

Entities | |

| MAPPED | architecture |

Libraries | |

| IEEE | |

Use Clauses | |

| STD_LOGIC_1164 | |

Ports | |

| RX_DATA | in std_logic_vector ( 15 downto 0 ) |

| RX_NOT_IN_TABLE | in std_logic_vector ( 1 downto 0 ) |

| RX_DISP_ERR | in std_logic_vector ( 1 downto 0 ) |

| RX_CHAR_IS_K | in std_logic_vector ( 1 downto 0 ) |

| RX_CHAR_IS_COMMA | in std_logic_vector ( 1 downto 0 ) |

| RX_BUF_ERR | in std_logic |

| TX_BUF_ERR | in std_logic |

| RX_REALIGN | in std_logic |

| RX_POLARITY | out std_logic |

| RX_RESET | out std_logic |

| TX_CHAR_IS_K | out std_logic_vector ( 1 downto 0 ) |

| TX_DATA | out std_logic_vector ( 15 downto 0 ) |

| TX_RESET | out std_logic |

| ENA_COMMA_ALIGN | out std_logic |

| GEN_SCP | in std_logic |

| GEN_ECP | in std_logic |

| GEN_PAD | in std_logic |

| TX_PE_DATA | in std_logic_vector ( 0 to 15 ) |

| TX_PE_DATA_V | in std_logic |

| GEN_CC | in std_logic |

| RX_PAD | out std_logic |

| RX_PE_DATA | out std_logic_vector ( 0 to 15 ) |

| RX_PE_DATA_V | out std_logic |

| RX_SCP | out std_logic |

| RX_ECP | out std_logic |

| GEN_A | in std_logic |

| GEN_K | in std_logic_vector ( 0 to 1 ) |

| GEN_R | in std_logic_vector ( 0 to 1 ) |

| GEN_V | in std_logic_vector ( 0 to 1 ) |

| LANE_UP | out std_logic |

| SOFT_ERR | out std_logic |

| HARD_ERR | out std_logic |

| CHANNEL_BOND_LOAD | out std_logic |

| GOT_A | out std_logic_vector ( 0 to 1 ) |

| GOT_V | out std_logic |

| USER_CLK | in std_logic |

| RESET_SYMGEN | in std_logic |

| RESET | in std_logic |

Definition at line 67 of file aurora_lane.vhd.