# TARGETC readout boards

Salvador Ventura

Jose Duron, Gary Varner, Kurtis Nishimura

HMB kick-off meeting 08-21-2020

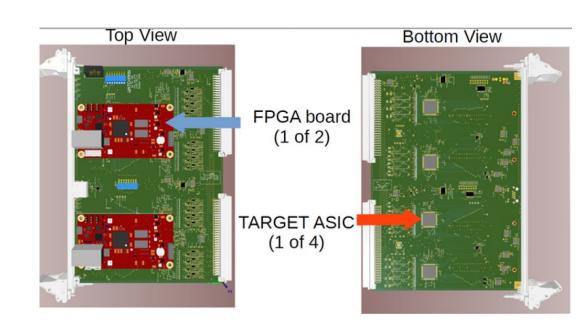

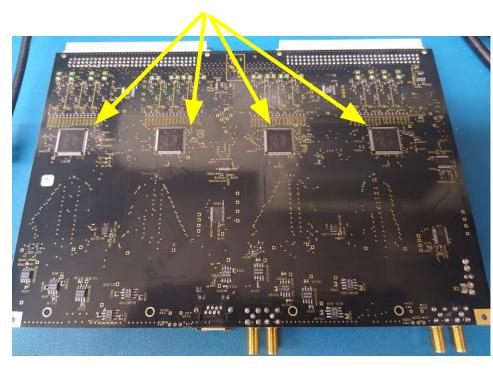

# 16U VME Card

- 4 TARGETCs

- 16 PMT inputs.

- Gain stages for each PMT input: :x10, x1, x1/10 and x1/100.

- 2 trigger mechanisms to improve sensitivity and minimize false triggers.

- 2 Microzed Boards, Zynq Z020

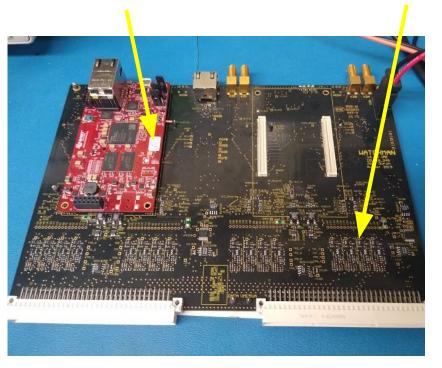

# TARGETC Readout for WATCHMAN

Microzed board Gain stages TARGETCs

## TARGETC Readout for WATCHMAN

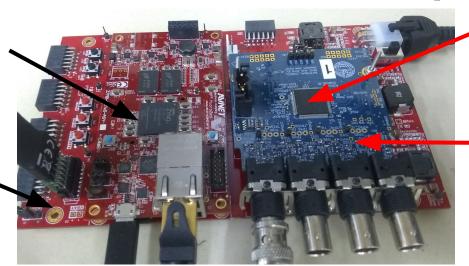

FMC Board

- **TARGETC.** A **1GSa/s, 12-bit, 16-channel** Wilkinson ADC, which was designed and fabricated by Gary Varner's ASIC group at UH-Manoa.

- -A **ZYNQ SoC** by Xilinx with an FPGA and a dual-core ARM processor.

MicroZed Board Zynq-7000 SOC FPGA+ ARM Proc.

FMC carrier board

x1, x10,x0.1 and x0.01 gain stages

#### Done:

### Firmware including:

- Interface with TARGETC

- Auto trigger algorithm: sel storage array address to write and windows to digitize from trigger signal.

- Data transfer

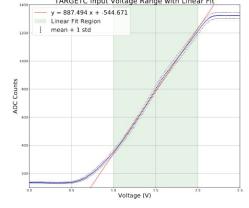

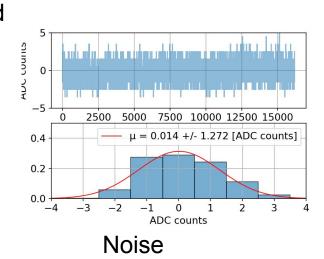

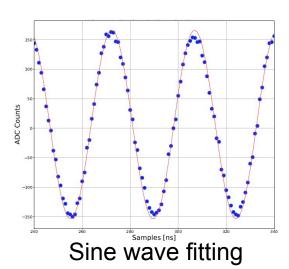

#### Dynamic range

4 PMT-channel FMC board characterization

#### **Current status:**

Migration from FMC board to VME board

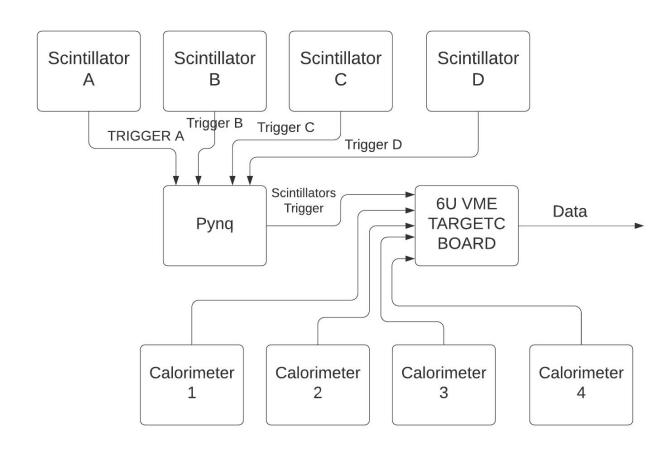

#### **Hawaii Muon Beamline**

## FPGA overlays – hardware libraries

Step 1:

Create an FPGA design for a <u>class</u> of related applications

```

wold settlement(stat, seres)_t(state, tat);

} decimate(stat, seres)_t(state, tat);

} setd settlement(stat, seres)_t(state, tat);

} setd settlement(stat, teneral, blocks, tat);

} set settlement(stat, teneral, teneral, tat);

int set, tat);

int set, tating;

setilement(state, tat);

settlement(state, tat);

settlement(state, tating);

settlement(st

```

Step 3:

Wrap the C API to create a Python library

Step 2:

Export the bitstream and a C API for programming the design

```

6C78 3963 7367 3232 3580 6308 8632

From time import sleep

from pure import Overlay

from pyro-iop import PPOD ACC, PHED DAG

6109

8120

ol - Overlay("buse.bit")

()besineb.lo

a writing values from a my to 2, av with step m.cv.

duc_id : int(input("Type in the PPOD ID of the DOC (i = 2): "))

add id = int(imput("Type in the PMOD ID of the ADC (1 ~ 2): "))

0101

dac - PMOD DAC(dac fd)

ade = PROD_ADC(adc_ld)

ushie + 0.1 * -

dac.write(value)

sleep(e.s)

readingenate, read(1, 0, 0)

alternational at

print("soltage read by S&C is: (1.4F) Volts", Toront(adc.read(1,8,8)[0]))

```

Step 4:

Import the bitstream and the library in your Python scripts and program