### example project to interface to M6800-style peripheral

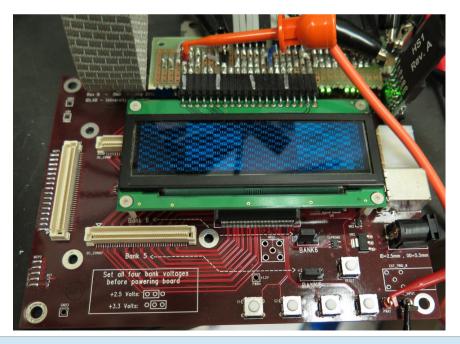

- OLED display control project:

- https://code.google.com/p/idlab-general/source/browse/universal\_eval/OLED\_display/

- clock\_enable\_generator:

- http://code.google.com/p/idlab-scrod/source/browse/SCRODboardstack/new dag interface/src/utilities/clock enable generator.vhd

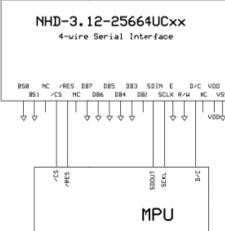

### example interface: OLED display (M6800)

MPU Interface Pin Assignment Summery

| Bus        |    | Data/Command Interface |    |    |      |      | Control Signals |         |     |         |      |      |      |

|------------|----|------------------------|----|----|------|------|-----------------|---------|-----|---------|------|------|------|

| Interface  | D7 | D6                     | D5 | D4 | D3   | D2   | D1              | D0      | E   | R/W     | /cs  | D/C  | /RES |

| 8-bit 6800 |    | D[7:0]                 |    |    |      |      |                 | Е       | R/W | /CS     | D/C  | /RES |      |

| 8-bit 8080 |    | D[7:0]                 |    |    |      |      |                 | /RD     | /WR | /CS     | D/C  | /RES |      |

| 3-wire SPI |    | Tie LOW                |    | NC | SDIN | SCLK | Tie LOW         |         | /CS | Tie LOW | /RES |      |      |

| 4-wire SPI |    | Tie LOW                |    |    | NC   | SDIN | SCLK            | Tie LOW |     | /CS     | D/C  | /RES |      |

- page 5 of datasheet:

- shows four interface options

- page 10:

- shows signal descriptions

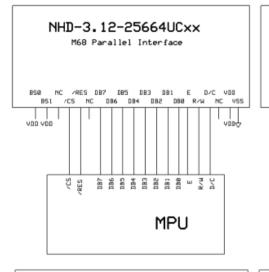

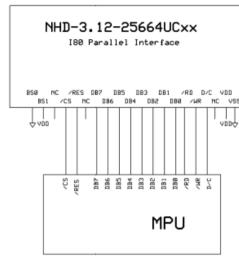

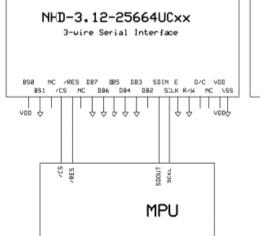

#### **Wiring Diagrams**

#### 6800-MPU Parallel Interface

The parallel interface consists of 8 bi-directional data pins, R/W, D/C, E, and /CS.

A LOW on R/W indicates write operation, and HIGH on R/W indicates read operation.

A LOW on D/C indicates "Command" read or write, and HIGH on D/C indicates "Data" read or write.

The E input serves as data latch signal, while /CS is LOW. Data is latched at the falling edge of E signal.

| Function      | E            | R/W | /cs | D/C |

|---------------|--------------|-----|-----|-----|

| Write Command | $\downarrow$ | 0   | 0   | 0   |

| Read Status   | <b>V</b>     | 1   | 0   | 0   |

| Write Data    | <b>+</b>     | 0   | 0   | 1   |

| Read Data     | 4            | 1   | 0   | 1   |

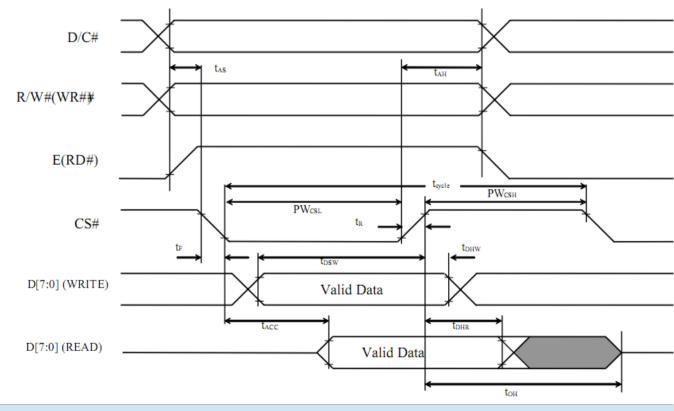

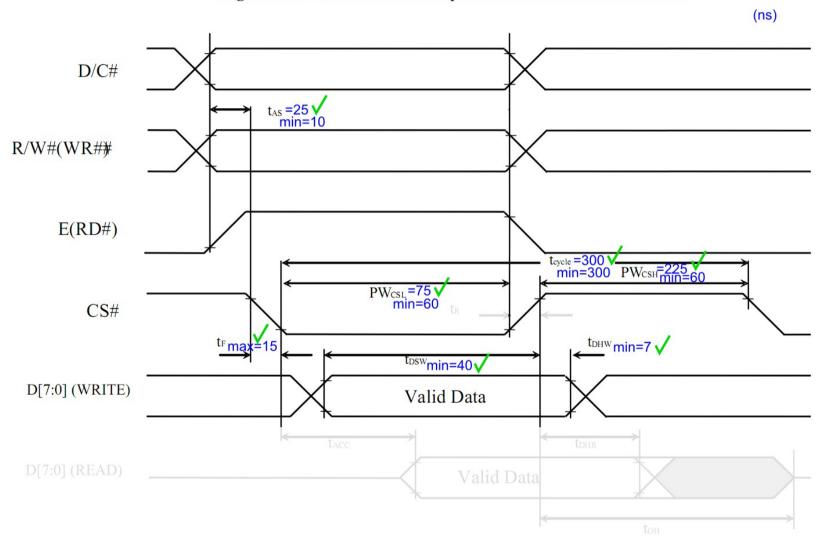

## OLED display timing

$(V_{DD} - V_{SS} = 2.4 \text{ to } 2.6 \text{V}, V_{DDIO} = 1.6 \text{V}, V_{CI} = 3.3 \text{V}, T_A = 25^{\circ}\text{C})$

| Symbol             | Parameter                            | Min | Тур | Max | Unit |

|--------------------|--------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -   | -   | ns   |

| $t_{DSW}$          | Write Data Setup Time                | 40  | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                 | 7   | -   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                  | 20  | -   | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | -   | 140 | ns   |

| $PW_{CSL}$         | Chip Select Low Pulse Width (read)   | 120 | -   | -   | ns   |

|                    | Chip Select Low Pulse Width (write)  | 60  |     |     |      |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (read)  | 60  | -   | -   | ns   |

|                    | Chip Select High Pulse Width (write) | 60  |     |     |      |

| t <sub>R</sub>     | Rise Time                            | -   | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                            | -   | -   | 15  | ns   |

page 51 of display transfer

controller's datasheet

Figure 13-1: 6800-series MCU parallel interface characteristics

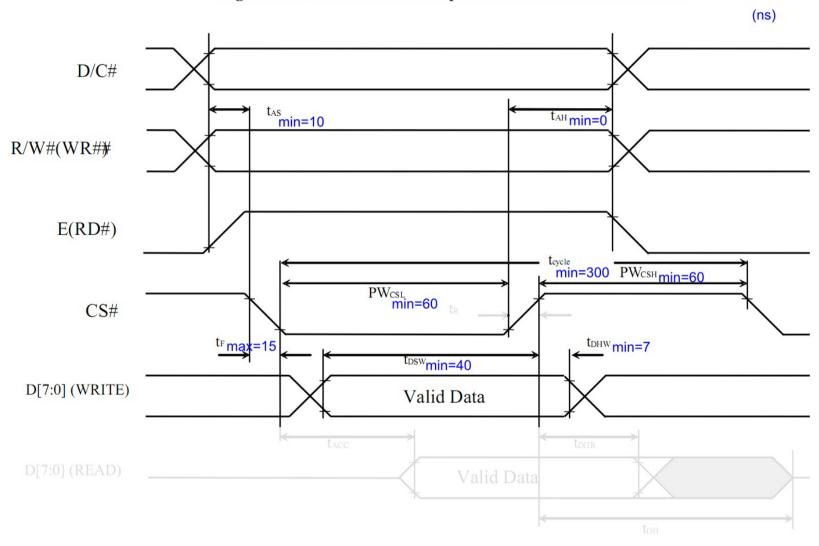

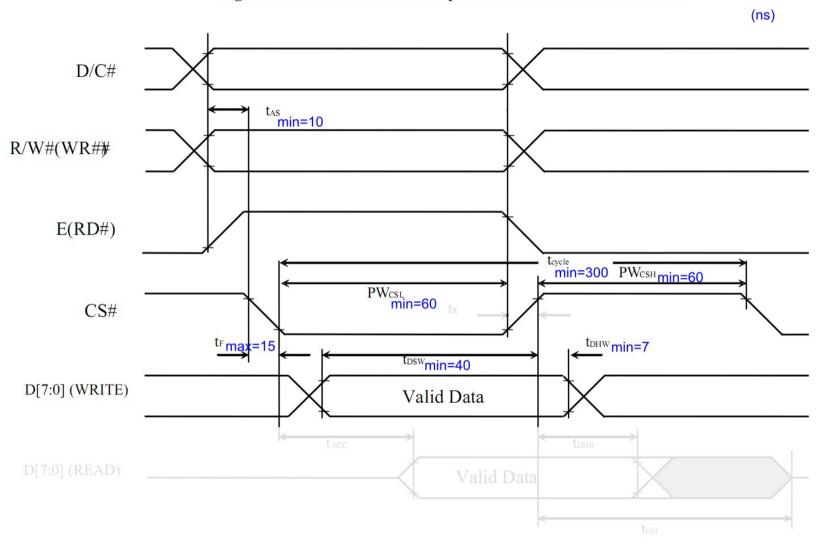

# OLED timing diagram (original)

Figure 13-1: 6800-series MCU parallel interface characteristics

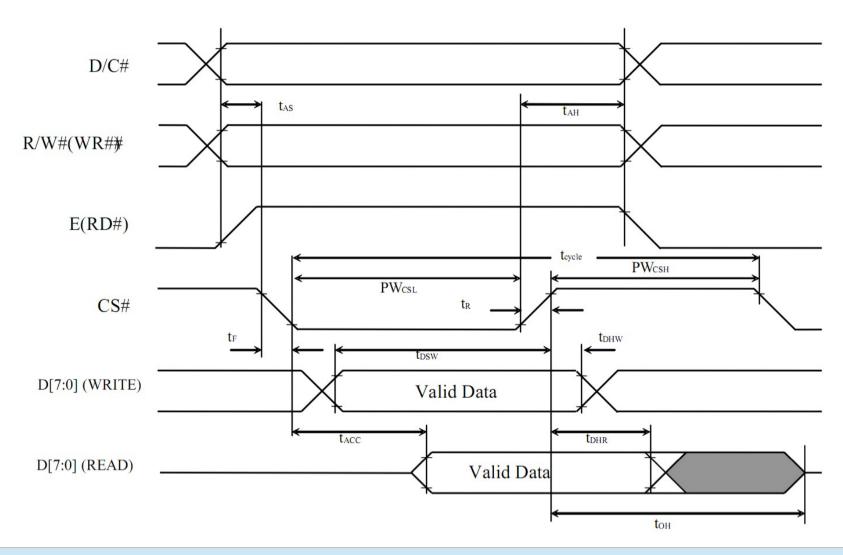

# OLED timing diagram (ignore irrelevant parts)

Figure 13-1: 6800-series MCU parallel interface characteristics

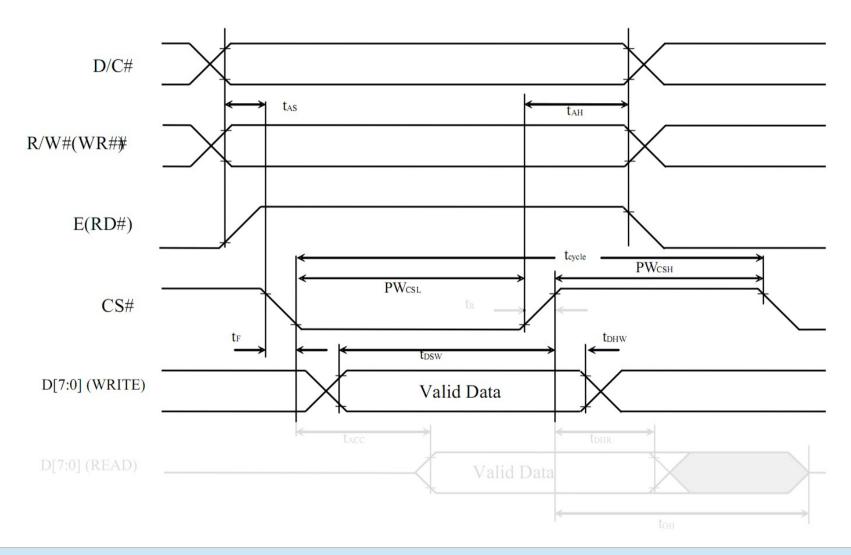

# OLED timing diagram (annotate with min/max constraints)

Figure 13-1: 6800-series MCU parallel interface characteristics

# OLED timing diagram (make adjustments to simplify)

Figure 13-1: 6800-series MCU parallel interface characteristics

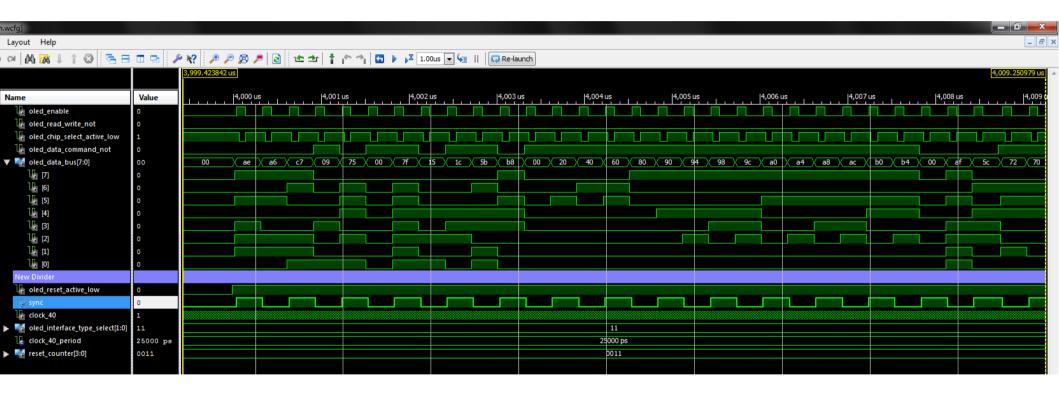

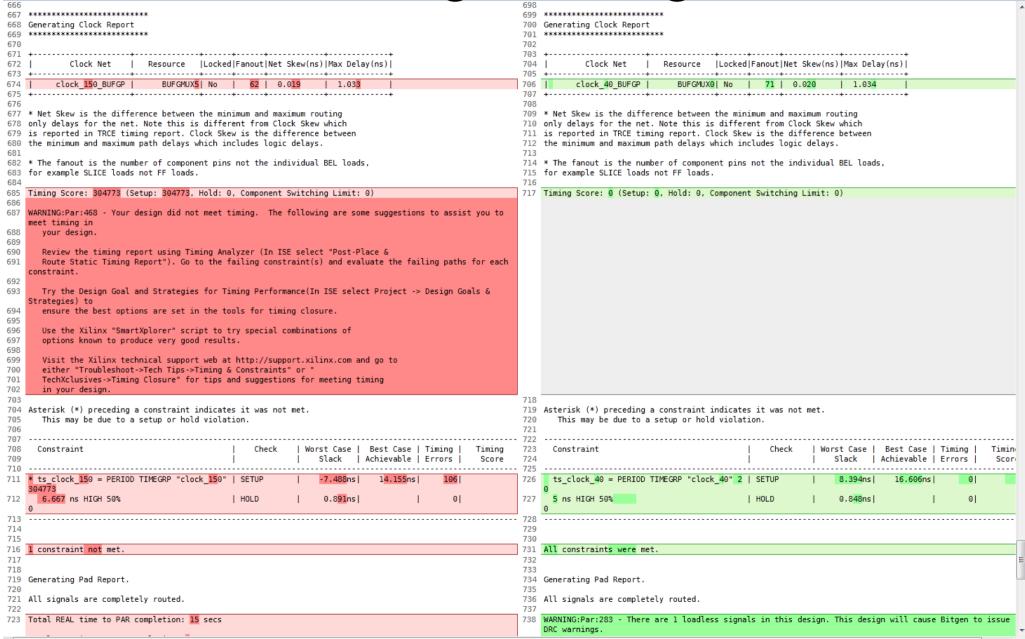

#### OLED display control loop

```

al\OLED_display\ise-project\OLED_display.xise - [OLED_display.vhdl]

t Help

if (transaction required = '1') then

if (individual transaction counter < 10) then -- total 300 ns cycle time

-- (takes a cycle to get here from elsewhere)

transaction in progress <= '1';

if (individual transaction counter < 1) then -- itc = 0 (for 25 ns)

internal sync <= not internal sync;

internal enable <= '1';

elsif (individual transaction counter < 4) then -- itc = 1, 2, 3 (for 75 ns)

internal chip select <= '1';

-- itc = 4, 5, 6, 7, 8, 9 (for 150 ns)

else

internal chip select <= '0';

internal enable <= '0';

end if:

individual transaction counter <= individual transaction counter + 1;

-- itc = 10 (for 25 ns)

else

transaction required <= '0';

transaction in progress <= '0';

individual transaction counter <= (others => '0');

end if:

end if:

```

#### testbench / simulation

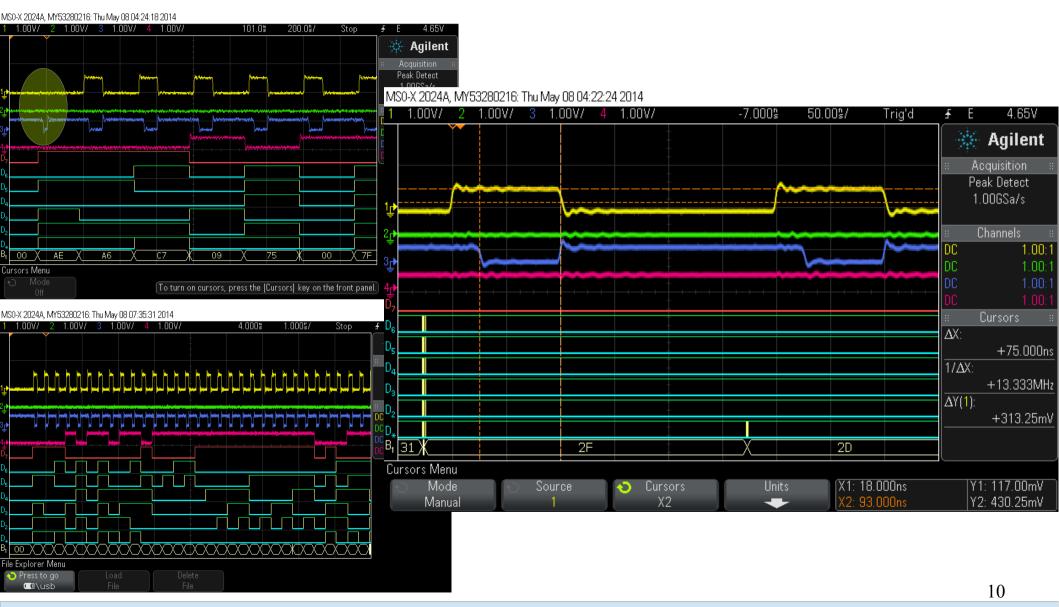

#### scope traces

# OLED timing diagram (verify met all requirements)

Figure 13-1: 6800-series MCU parallel interface characteristics

#### advice

```

entity Xample is

constant mywidth : integer := 8

port

std logic;

inout std logic vector (mywidth-1 downto 0);

out std logic

```

- use constants where possible:

- to reduce instances of "magic numbers:"

- constant mywidth : integer := integer(ceil(log2(1300.0)));

- for future expandability:

- signal mycounter : unsigned(mywidth-1 downto 0);

- better yet, use generics!

- don't be intimidated by the flurry of messages that go by as it compiles

```

entity work.Xample

mywidth => db width

clock

=> clk,

```

pay attention to the warnings that are your fault; these are clues as to what you are doing wrong

warning messages

#### more advice

- don't use up all the global clocks; use a single clock and distribute clock enables with the appropriate duty cycles

- read through coding recommendations from Xilinx (and follow them!):

- http://www.xilinx.com/support/documentation/sw\_manuals/xilinx14\_7/sim.pdf

- http://www.xilinx.com/support/documentation/sw\_manuals/xilinx14\_7/xst\_v6s6.pdf

- if possible, use someone else's working code

- build things one at a time and <u>test them!</u>

#### parting words...

A complex system that works is invariably found to have evolved from a simple system that worked. A complex system designed from scratch never works and cannot be patched up to make it work. You have to start over with a working simple system. – John Gall (1975)