## Digital Circuit for Optical Module

Toshifumi Aoki (ICRR, Japan)

and

Japan DUMAND Collaboration

### Introduction

We have chosen the one-chip microcomputer TMP68301 (Toshiba) as the CPU in OM, taking into account the following requirements:

- (1) One of 68000 series, because 68000 will be used in SBC.

- (2) low power consumption (CMOS).

- (3) compact.

5560 660

经销售

414.00

(4) easy to connect external devices.

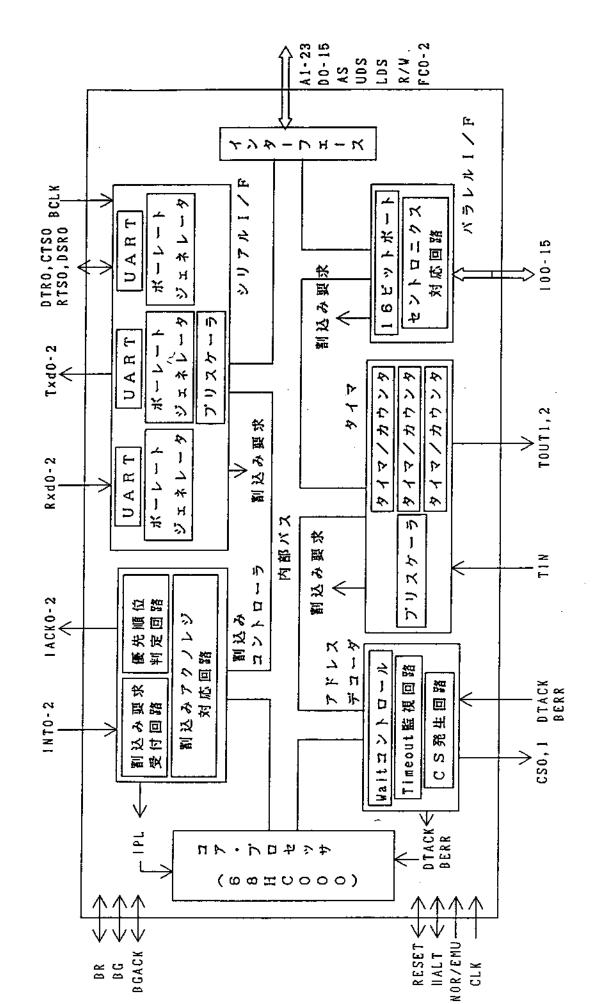

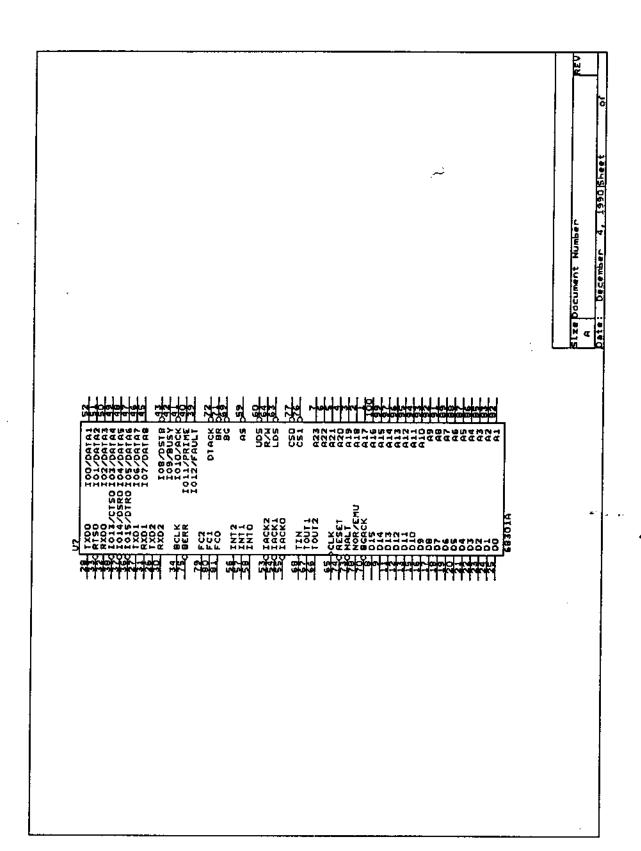

TMP68301 consists of a core processor 68HC000 (CMOS version of 68000) and peripheral devices around it. Those are three serial I/F's, a parallel I/F, an external bus I/F, timers, an address decoder and so on. The block diagram inside the chip is shown in Fig. 1 (in Japanese).

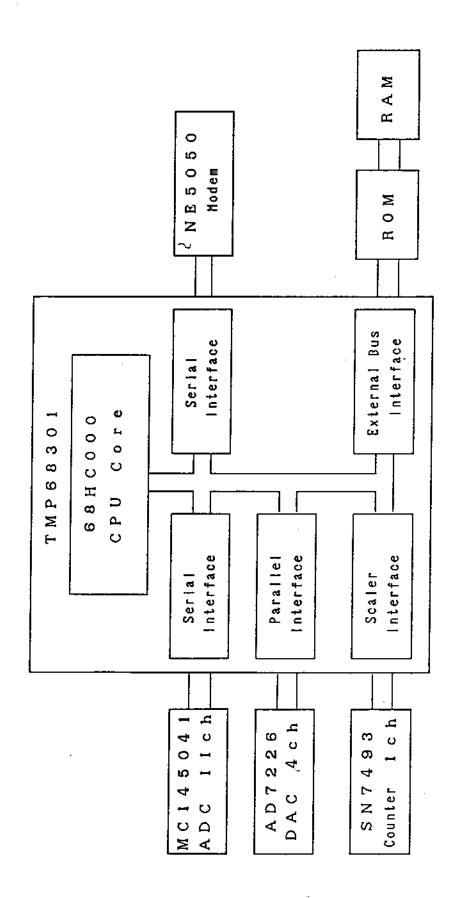

The connections of external devices necessary for OM are considered so as to use the internal devices effectively. In Fig. 2, our rough idea is shown. There are still a few unsolved problems, so Fig. 2 may not be the final version.

### ROM

Since ROM is used only for the bootstrap program when the power is turned on, we do not need much memory. The ROM is located at the zero address only at the time of power-on or reset, and usually located at the rear of RAM in the address space. This can be realized without any extra decoder, by managing the resister in the CS (Chip Select) generator. Fig. 4 shows our ROM interface circuit. Only one chip of ROM is enough for our purpose, and then a 8-bit latch is put in front of ROM to make it accessible in unit of word (16-bit).

### RAM

A pair of RAM accessible in unit of word is designed, because small package-type SRAM is available which makes a high density mounting possible.

The internal decoder is also used like in the case of ROM. Our RAM interface circuit is shown in Fig. 5.

#### ADC

If we adopt a kind of ADC with serial 10, we can utilize serial ports in 68301 effectively, and can make the ocuppying space on the board smaller. But, a further idea is needed with respect to its interface. The upper one in Fig. 6 is a serial ADC.

#### DAC

The DAC chip we are going to use is made of CMOS and has four channels. It is connected directly to the parallel interface in 68301 and can be easily controlled by generating a parallel output of both data and channel assignment signal. The lower one in Fig. 6 is DAC.

## Modem Circuit

Modem can be connected directly to one of three serial ports in 68301 and its parameters can be set through software. V. Commichau (Aachen) is developing a detailed design using a power line modem NE5050 (Signetics/ Valvo). M. Mignard (Hawaii) seems to have another idea of design. We may be able to follow their results.

# Scaler Circuit

Using a 16-bit scaler and a timer inside 68301, the PMT count rate etc. can be measured.

To develope the circuit, we have purchased a personal computer PC9801(NEC), and a few softwares; OrCADs' for drawing the circuit diagram and for designing the print board, a cross assembler and cross compiler for 68000, etc.

\*\*\*

F18.1 Block Diagram inside TMP68301

18688844

F18.2 Peripheral Devices for Optical Module

1. 186

Fig. 4 ROM

Fig. 5 RAM

Fig.6 ADC and DAC