### Today's agenda (2-FEB-2010)

- Will check your web page (links), which should include

- Block diagram

- Acronym (what it is called)

- Schedule outline

- Description paragraph

- To be augmented with table of specifications

- IBM submission updates

#### Suggested Milestones

- Specification Review [Feb 15]

- Complete schematics

- Block diagram

- Table of key parameters

- Design Readiness Review [March 1-14]

- Design simulations, iteration

- Confirmation of key parameters

- Begin Layout [March 15]

- Floorplanning

- All April to complete layout

- LVS checks during hierarchy build

- Post layout simulations

- Final Design Review [early May]

- Compile documentation, hold review

- Final confirmation of key parameters

#### Outline

- Scaling

- Transistors

- Interconnect

- Future Challenges

- VLSI Economics

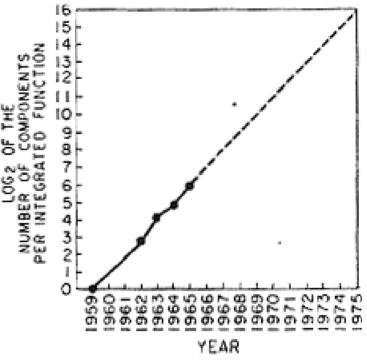

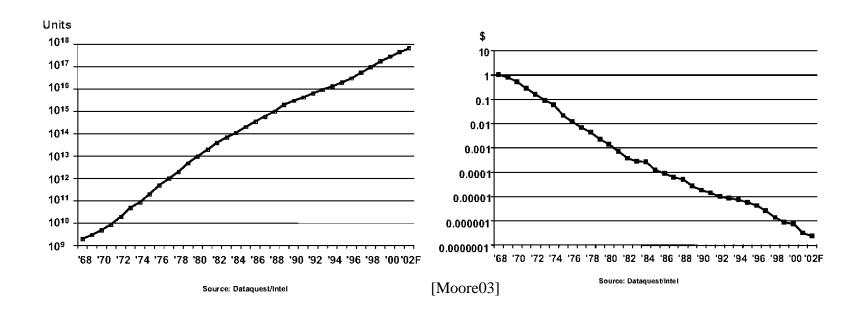

#### Moore's Law

• In 1965, Gordon Moore predicted the exponential growth of the number of

transistors on an IC

Transistor count doubled every year since invention

Predicted > 65,000 transistors by 1975!

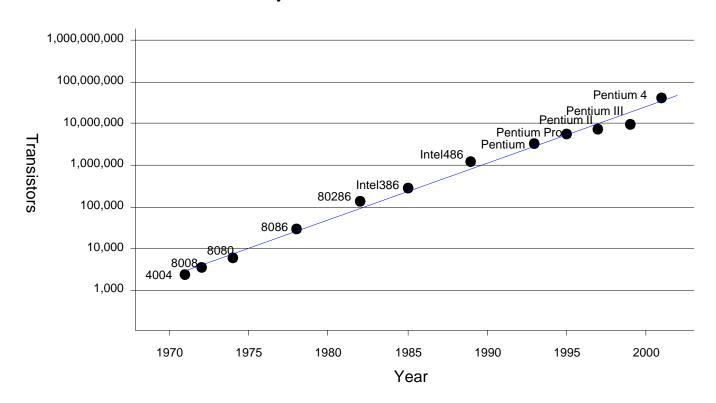

#### More Moore

Transistor counts have doubled every 26 months for the past three decades.

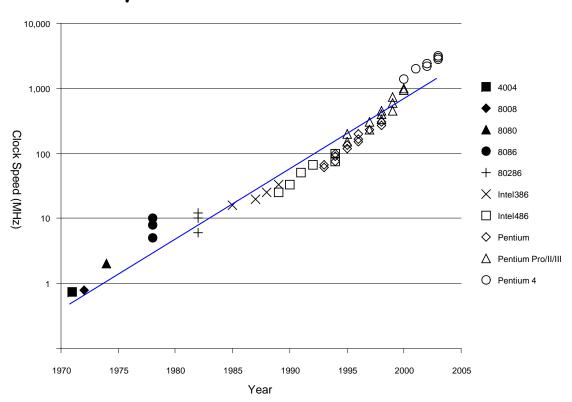

### Speed Improvement

- Clock frequencies have also increased exponentially

- A corollary of Moore's Law

### Why?

Why more transistors per IC?

Why faster computers?

### Why?

- Why more transistors per IC?

- Smaller transistors

- Larger dice

- Why faster computers?

#### Why?

- Why more transistors per IC?

- Smaller transistors

- Larger dice

- Why faster computers?

- Smaller, faster transistors

- Better microarchitecture (more IPC)

- Fewer gate delays per cycle

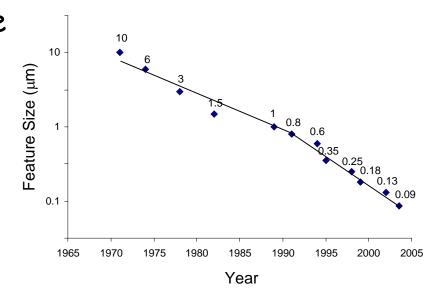

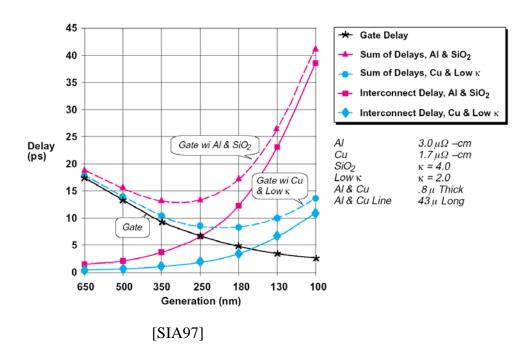

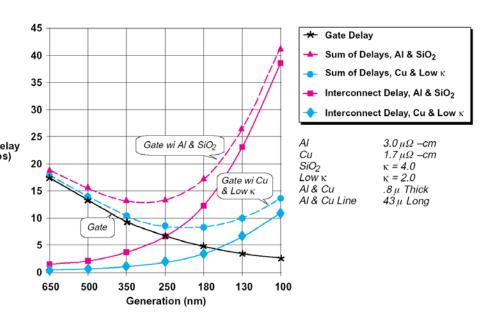

### Scaling

- The only constant in VLSI is constant change

- · Feature size shrinks by 30% every 2-3 years

- Transistors become cheaper

- Transistors become faster

- Wires do not improve (and may get worse)

- Scale factor S

- Typically  $S = \sqrt{2}$

- Technology nodes

#### Scaling Assumptions

- What changes between technology nodes?

- Constant Field Scaling

- All dimensions (x, y, z => W, L, tox)

- Voltage (V<sub>DD</sub>)

- Doping levels

- Lateral Scaling

- Only gate length L

- Often done as a quick gate shrink (S = 1.05)

| Table 4.45 Influence of surlivers       | NOC design                                                    | -lt               |         |  |  |

|-----------------------------------------|---------------------------------------------------------------|-------------------|---------|--|--|

|                                         | Table 4.15 Influence of scaling on MOS device characteristics |                   |         |  |  |

| Parameter                               | Sensitivity                                                   | Constant<br>Field | Lateral |  |  |

| Scaling                                 | Parameters                                                    |                   |         |  |  |

| Length: $L$                             |                                                               |                   |         |  |  |

| Width: W                                |                                                               |                   |         |  |  |

| Gate oxide thickness: $t_{ox}$          |                                                               |                   |         |  |  |

| Supply voltage: $V_{DD}$                |                                                               | <b>T</b>          |         |  |  |

| Threshold voltage: $V_{tn}$ , $V_{tp}$  |                                                               | Ţ                 |         |  |  |

| Substrate doping: $N_A$                 |                                                               | T                 |         |  |  |

| Device C                                | haracteristics                                                |                   |         |  |  |

| β                                       |                                                               |                   |         |  |  |

|                                         |                                                               |                   |         |  |  |

| Current: $I_{ds}$                       |                                                               |                   |         |  |  |

|                                         |                                                               |                   |         |  |  |

| Resistance: R                           |                                                               |                   |         |  |  |

|                                         |                                                               |                   |         |  |  |

| Gate capacitance: C                     |                                                               | 1                 |         |  |  |

|                                         |                                                               |                   |         |  |  |

|                                         |                                                               |                   |         |  |  |

| Gate delay: τ                           |                                                               |                   |         |  |  |

| Clock frequency: f                      |                                                               |                   |         |  |  |

| Dynamic power dissipation (per gate): P | -                                                             |                   |         |  |  |

| Chip area: A                            |                                                               |                   |         |  |  |

| Power density                           |                                                               |                   |         |  |  |

| Current density                         |                                                               |                   |         |  |  |

| Table 4.45 Influence of maline               | MOC design     | -l       | :       |

|----------------------------------------------|----------------|----------|---------|

| Table 4.15 Influence of scaling or Parameter | Sensitivity    | Constant | Lateral |

|                                              |                | Field    |         |

| Scaling                                      | Parameters     |          |         |

| Length: $L$                                  |                | 1/S      | 1/S     |

| Width: W                                     |                | 1/S      | 1       |

| Gate oxide thickness: $t_{ox}$               |                | 1/S      | 1       |

| Supply voltage: $V_{DD}$                     |                | 1/S      | 1       |

| Threshold voltage: $V_{tn}$ , $V_{tp}$       |                | 1/S      | 1       |

| Substrate doping: $N_A$                      |                | S        | 1       |

| Device C                                     | naracteristics |          |         |

| β                                            |                |          |         |

|                                              |                |          |         |

| Current: $I_{ds}$                            |                |          |         |

| Resistance: R                                |                |          |         |

| Gate capacitance: C                          |                |          |         |

| Gate delay: τ                                |                |          |         |

| Clock frequency: f                           |                |          |         |

| Dynamic power dissipation (per gate): P      |                |          |         |

| Chip area: A                                 | -              |          |         |

| Power density                                |                |          |         |

| Current density                              |                |          |         |

| Table 4.15 Influence of scaling on MOS device characteristics |                                       |                   |         |

|---------------------------------------------------------------|---------------------------------------|-------------------|---------|

| Parameter                                                     | Sensitivity                           | Constant<br>Field | Lateral |

| Scaling                                                       | Parameters                            |                   |         |

| Length: $L$                                                   |                                       | 1/S               | 1/S     |

| Width: W                                                      |                                       | 1/S               | 1       |

| Gate oxide thickness: $t_{ox}$                                |                                       | 1/S               | 1       |

| Supply voltage: $V_{DD}$                                      |                                       | 1/S               | 1       |

| Threshold voltage: $V_{tn}$ , $V_{tp}$                        |                                       | 1/S               | 1       |

| Substrate doping: $N_A$                                       |                                       | S                 | 1       |

| Device Cl                                                     | haracteristics                        |                   |         |

| β                                                             | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S       |

| Current: $I_{ds}$                                             |                                       |                   |         |

| Resistance: R                                                 |                                       |                   |         |

| Gate capacitance: C                                           |                                       | ,                 |         |

| Gate delay: τ                                                 |                                       |                   |         |

| Clock frequency: f                                            |                                       |                   |         |

| Dynamic power dissipation (per gate): P                       |                                       |                   |         |

| Chip area: A                                                  | -                                     | '                 | '       |

| Power density                                                 |                                       |                   |         |

| Current density                                               |                                       |                   |         |

| Table 4.15 Influence of scaling or      | MOS device o                          | haracterist       | ics     |

|-----------------------------------------|---------------------------------------|-------------------|---------|

| Parameter Parameter                     | Sensitivity                           | Constant<br>Field | Lateral |

| Scaling                                 | Parameters                            | !                 |         |

| Length: $L$                             |                                       | 1/S               | 1/S     |

| Width: W                                |                                       | 1/S               | 1       |

| Gate oxide thickness: $t_{ox}$          |                                       | 1/S               | 1       |

| Supply voltage: $V_{DD}$                |                                       | 1/S               | 1       |

| Threshold voltage: $V_{tn}$ , $V_{tp}$  |                                       | 1/S               | 1       |

| Substrate doping: $N_{A}$               |                                       | S                 | 1       |

| Device CI                               | naracteristics                        |                   |         |

| β                                       | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S       |

| Current: $I_{ds}$                       | $\beta \big(V_{DD}-V_t\big)^2$        | 1/S               | S       |

| Resistance: R                           |                                       |                   |         |

| Gate capacitance: C                     |                                       |                   |         |

| Gate delay: τ                           |                                       |                   |         |

| Clock frequency: f                      |                                       |                   |         |

| Dynamic power dissipation (per gate): P |                                       |                   |         |

| Chip area: A                            | -                                     |                   |         |

| Power density                           |                                       |                   |         |

| Current density                         |                                       |                   |         |

| Table 4.15 Influence of scaling on MOS device characteristics |                                       |                   |         |

|---------------------------------------------------------------|---------------------------------------|-------------------|---------|

| Parameter                                                     | Sensitivity                           | Constant<br>Field | Lateral |

| Scaling                                                       | Parameters                            |                   | ·       |

| Length: $L$                                                   |                                       | 1/S               | 1/S     |

| Width: W                                                      |                                       | 1/S               | 1       |

| Gate oxide thickness: $t_{ox}$                                |                                       | 1/S               | 1       |

| Supply voltage: $V_{DD}$                                      |                                       | 1/S               | 1       |

| Threshold voltage: $V_{tn}$ , $V_{tp}$                        |                                       | 1/S               | 1       |

| Substrate doping: $N_A$                                       |                                       | S                 | 1       |

| Device C                                                      | haracteristics                        |                   |         |

| β                                                             | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S       |

| Current: $I_{ds}$                                             | $\beta \big( V_{DD} - V_t \big)^2$    | 1/S               | S       |

| Resistance: R                                                 | $rac{{V_{DD}}}{{I_{ds}}}$            | 1                 | 1/S     |

| Gate capacitance: C                                           |                                       |                   |         |

| Gate delay: τ                                                 |                                       |                   |         |

| Clock frequency: f                                            | Ť                                     |                   |         |

| Dynamic power dissipation (per gate): P                       |                                       |                   |         |

| Chip area: A                                                  |                                       | 1                 | '       |

| Power density                                                 |                                       |                   |         |

| Current density                                               |                                       | '                 | '       |

| m-1-1- 4.45 1-40                        | MOC Ind                               | 1        | •       |

|-----------------------------------------|---------------------------------------|----------|---------|

| Table 4.15 Influence of scaling or      |                                       | Constant | Lateral |

| Parameter                               | Sensitivity                           | Field    | Lateral |

| Scaling                                 | Parameters                            |          |         |

| Length: $L$                             |                                       | 1/S      | 1/S     |

| Width: W                                |                                       | 1/S      | 1       |

| Gate oxide thickness: $t_{ox}$          |                                       | 1/S      | 1       |

| Supply voltage: $V_{DD}$                |                                       | 1/S      | 1       |

| Threshold voltage: $V_{tn}$ , $V_{tp}$  |                                       | 1/S      | 1       |

| Substrate doping: $N_A$                 |                                       | S        | 1       |

| Device Cl                               | haracteristics                        |          |         |

| β                                       | <i>W</i> 1                            | S        | S       |

|                                         | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ |          |         |

| Current: $I_{ds}$                       | $\beta \big(V_{DD}-V_{t}\big)^{2}$    | 1/S      | S       |

| Resistance: R                           | $rac{V_{DD}}{I_{ds}}$                | 1        | 1/8     |

| Gate capacitance: C                     | $\frac{WL}{t_{ m ox}}$                | 1/S      | 1/S     |

| Gate delay: τ                           |                                       |          | '       |

| Clock frequency: f                      |                                       |          |         |

| Dynamic power dissipation (per gate): P |                                       |          |         |

| Chip area: $\Lambda$                    | -                                     |          | '       |

| Power density                           |                                       |          |         |

| Current density                         |                                       |          |         |

| m 11 445 1 0 C - N                                            | 1100 1                                |                   |           |  |

|---------------------------------------------------------------|---------------------------------------|-------------------|-----------|--|

| Table 4.15 Influence of scaling on MOS device characteristics |                                       |                   |           |  |

| Parameter                                                     | Sensitivity                           | Constant<br>Field | Lateral   |  |

| Scaling                                                       | Parameters                            |                   | •         |  |

| Length: $L$                                                   |                                       | 1/S               | 1/S       |  |

| Width: W                                                      |                                       | 1/S               | 1         |  |

| Gate oxide thickness: $t_{ m ox}$                             |                                       | 1/S               | 1         |  |

| Supply voltage: $V_{DD}$                                      |                                       | 1/S               | 1         |  |

| Threshold voltage: $V_{tn}$ , $V_{tp}$                        |                                       | 1/S               | 1         |  |

| Substrate doping: $N_A$                                       |                                       | S                 | 1         |  |

| Device Cl                                                     | naracteristics                        |                   |           |  |

| β                                                             | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S         |  |

| Current: $I_{ds}$                                             | $\beta \big(V_{DD}-V_{t}\big)^{2}$    | 1/S               | S         |  |

| Resistance: R                                                 | $rac{V_{DD}}{I_{ds}}$                | 1                 | 1/S       |  |

| Gate capacitance: C                                           | $\frac{WL}{t_{ m ox}}$                | 1/S               | 1/S       |  |

| Gate delay: τ                                                 | RC                                    | 1/S               | $1/S^{2}$ |  |

| Clock frequency: f                                            |                                       |                   |           |  |

| Dynamic power dissipation (per gate): P                       |                                       |                   |           |  |

| Chip area: A                                                  | -                                     | '                 |           |  |

| Power density                                                 |                                       |                   |           |  |

| Current density                                               |                                       |                   |           |  |

| Parameter                               | Sensitivity                           | Constant<br>Field | Lateral     |

|-----------------------------------------|---------------------------------------|-------------------|-------------|

| Scaling                                 | Parameters                            |                   |             |

| Length: $L$                             |                                       | 1/S               | 1/ <i>S</i> |

| Width: W                                |                                       | 1/S               | 1           |

| Gate oxide thickness: $t_{ox}$          |                                       | 1/S               | 1           |

| Supply voltage: $V_{DD}$                |                                       | 1/S               | 1           |

| Threshold voltage: $V_{tn}$ , $V_{tp}$  |                                       | 1/S               | 1           |

| Substrate doping: $N_A$                 |                                       | S                 | 1           |

| Device C                                | haracteristics                        |                   |             |

| β                                       | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S           |

| Current: $I_{ds}$                       | $\beta \big(V_{DD}-V_{t}\big)^{2}$    | 1/S               | S           |

| Resistance: R                           | $rac{V_{DD}}{I_{ds}}$                | 1                 | 1/S         |

| Gate capacitance: C                     | $\frac{WL}{t_{ m ox}}$                | 1/S               | 1/S         |

| Gate delay: τ                           | RC                                    | 1/ <i>S</i>       | $1/S^{2}$   |

| Clock frequency: f                      | 1/τ                                   | S                 | $S^2$       |

| Dynamic power dissipation (per gate): P |                                       |                   |             |

| Chip area: A                            |                                       |                   | ·           |

| Power density                           |                                       |                   |             |

| Current density                         |                                       |                   |             |

| Table 4.15 Influence of scaling on MOS device characteristics |                                       |                   |           |

|---------------------------------------------------------------|---------------------------------------|-------------------|-----------|

| Parameter                                                     | Sensitivity                           | Constant<br>Field | Lateral   |

| Scaling                                                       | Parameters                            |                   | •         |

| Length: $L$                                                   |                                       | 1/S               | 1/S       |

| Width: W                                                      |                                       | 1/S               | 1         |

| Gate oxide thickness: $t_{ m ox}$                             |                                       | 1/S               | 1         |

| Supply voltage: $V_{DD}$                                      |                                       | 1/S               | 1         |

| Threshold voltage: $V_{tn}$ , $V_{tp}$                        |                                       | 1/S               | 1         |

| Substrate doping: $N_A$                                       |                                       | S                 | 1         |

| Device C                                                      | haracteristics                        |                   |           |

| β                                                             | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S         |

| Current: $I_{ds}$                                             | $\beta \big( V_{DD} - V_t \big)^2$    | 1/S               | S         |

| Resistance: R                                                 | $rac{V_{DD}}{I_{ds}}$                | 1                 | 1/8       |

| Gate capacitance: C                                           | $\frac{WL}{t_{ m ox}}$                | 1/S               | 1/S       |

| Gate delay: τ                                                 | RC                                    | 1/S               | $1/S^{2}$ |

| Clock frequency: f                                            | 1/τ                                   | S                 | $S^2$     |

| Dynamic power dissipation (per gate): P                       | $CV^2f$                               | $1/S^2$           | S         |

| Chip area: A                                                  |                                       |                   | '         |

| Power density                                                 |                                       |                   |           |

| Current density                                               |                                       |                   |           |

| Parameter                               | Sensitivity                           | Constant<br>Field | Lateral   |

|-----------------------------------------|---------------------------------------|-------------------|-----------|

| Scaling                                 | Parameters                            |                   |           |

| Length: L                               |                                       | 1/S               | 1/S       |

| Width: W                                |                                       | 1/S               | 1         |

| Gate oxide thickness: $t_{ m ox}$       |                                       | 1/S               | 1         |

| Supply voltage: $V_{DD}$                |                                       | 1/S               | 1         |

| Threshold voltage: $V_{tn}$ , $V_{tp}$  |                                       | 1/S               | 1         |

| Substrate doping: $N_A$                 |                                       | S                 | 1         |

| Device C                                | haracteristics                        |                   |           |

| β                                       | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S         |

| Current: $I_{ds}$                       | $\beta \big(V_{DD}-V_{t}\big)^{2}$    | 1/S               | S         |

| Resistance: R                           | $rac{V_{DD}}{I_{ds}}$                | 1                 | 1/S       |

| Gate capacitance: C                     | $\frac{WL}{t_{ m ox}}$                | 1/S               | 1/S       |

| Gate delay: τ                           | RC                                    | 1/ <i>S</i>       | $1/S^{2}$ |

| Clock frequency: f                      | 1/τ                                   | S                 | $S^2$     |

| Dynamic power dissipation (per gate): P | $CV^2f$                               | $1/S^2$           | S         |

| Chip area: A                            | -                                     | $1/S^2$           | 1         |

| Power density                           |                                       |                   |           |

| Current density                         |                                       |                   |           |

| Parameter                                 | Sensitivity                           | Constant    | Lateral     |

|-------------------------------------------|---------------------------------------|-------------|-------------|

|                                           |                                       | Field       |             |

| Scaling                                   | Parameters                            |             |             |

| Length: $L$                               |                                       | 1/ <i>S</i> | 1/ <i>S</i> |

| Width: W                                  |                                       | 1/S         | 1           |

| Gate oxide thickness: $t_{ox}$            |                                       | 1/S         | 1           |

| Supply voltage: $V_{DD}$                  |                                       | 1/S         | 1           |

| Threshold voltage: $V_{tn}$ , $V_{tp}$    |                                       | 1/S         | 1           |

| Substrate doping: $N_A$                   |                                       | S           | 1           |

|                                           | haracteristics                        |             |             |

| β                                         | W 1                                   | S           | S           |

|                                           | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ |             |             |

| Current: $I_{ds}$                         | $\beta (V_{DD} - V_t)^2$              | 1/S         | S           |

|                                           | $\beta(V_{DD}-V_t)$                   |             |             |

| Resistance: R                             | V                                     | 1           | 1/ <i>S</i> |

|                                           | $rac{V_{DD}}{I_{ds}}$                |             |             |

| Gate capacitance: C                       |                                       | 1/S         | 1/ <i>S</i> |

| 1                                         | $\frac{WL}{t_{\text{ox}}}$            |             |             |

| 0                                         |                                       | 4./5        | 4.102       |

| Gate delay: τ                             | RC                                    | 1/ <i>S</i> | $1/S^2$     |

| Clock frequency: f                        | 1/τ                                   | S           | $S^2$       |

| Dynamic power dissipation (per gate): $P$ | $CV^2f$                               | $1/S^2$     | S           |

| Chip area: A                              |                                       | $1/S^2$     | 1           |

| Power density                             | P/A                                   | 1           | S           |

| Current density                           |                                       |             |             |

| Table 4.15 Influence of scaling on MOS device characteristics |                                       |                   |           |  |

|---------------------------------------------------------------|---------------------------------------|-------------------|-----------|--|

| Parameter                                                     | Sensitivity                           | Constant<br>Field | Lateral   |  |

| Scaling                                                       | Parameters                            |                   |           |  |

| Length: $L$                                                   |                                       | 1/S               | 1/S       |  |

| Width: W                                                      |                                       | 1/S               | 1         |  |

| Gate oxide thickness: $t_{ m ox}$                             |                                       | 1/S               | 1         |  |

| Supply voltage: $V_{DD}$                                      |                                       | 1/S               | 1         |  |

| Threshold voltage: $V_{tn}$ , $V_{tp}$                        |                                       | 1/S               | 1         |  |

| Substrate doping: $N_A$                                       |                                       | S                 | 1         |  |

| Device C                                                      | haracteristics                        |                   |           |  |

| β                                                             | $\frac{W}{L} \frac{1}{t_{\text{ox}}}$ | S                 | S         |  |

| Current: $I_{ds}$                                             | $\beta \big(V_{DD}-V_t\big)^2$        | 1/S               | S         |  |

| Resistance: R                                                 | $rac{V_{DD}}{I_{ds}}$                | 1                 | 1/S       |  |

| Gate capacitance: C                                           | $\frac{WL}{t_{\text{ox}}}$            | 1/S               | 1/S       |  |

| Gate delay: τ                                                 | RC                                    | 1/S               | $1/S^{2}$ |  |

| Clock frequency: f                                            | 1/τ                                   | S                 | $S^2$     |  |

| Dynamic power dissipation (per gate): P                       | $CV^2f$                               | $1/S^2$           | S         |  |

| Chip area: $\Lambda$                                          |                                       | $1/S^2$           | 1         |  |

| Power density                                                 | P/A                                   | 1                 | S         |  |

| Current density                                               | $I_{ds}/A$                            | S                 | S         |  |

#### Observations

- Gate capacitance per micron is nearly independent of process

- But ON resistance \* micron improves with process

- Gates get faster with scaling (good)

- Dynamic power goes down with scaling (good)

- Current density goes up with scaling (bad)

- Velocity saturation makes lateral scaling unsustainable

### Example

- Gate capacitance is typically about 2 fF/µm

- The FO4 inverter delay in the TT corner for a process of feature size f (in nm) is about 0.5 f ps

- Estimate the ON resistance of a unit (4/2  $\lambda$ ) transistor.

#### Solution

- Gate capacitance is typically about 2 fF/µm

- The FO4 inverter delay in the TT corner for a process of feature size f (in nm) is about 0.5f ps

- Estimate the ON resistance of a unit (4/2  $\lambda$ ) transistor.

- FO4 =  $5 \tau = 15 RC$

- RC = (0.5f) / 15 = (f/30) ps/nm

- If W = 2f, R = 8.33 k $\Omega$

- Unit resistance is roughly independent of f

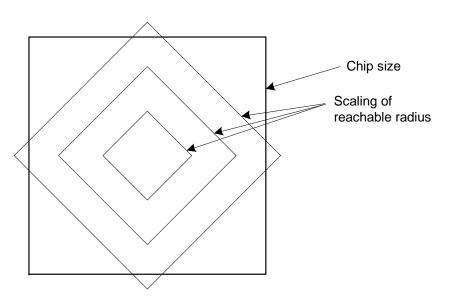

### Scaling Assumptions

- Wire thickness

- Hold constant vs. reduce in thickness

- · Wire length

- Local / scaled interconnect

- Global interconnect

- Die size scaled by  $D_c \approx 1.1$

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                    |                      |                       |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------|--|--|--|

| Parameter                                                                                                 | Sensitivity        | Reduced<br>Thickness | Constant<br>Thickness |  |  |  |

| Scaling Pa                                                                                                | Scaling Parameters |                      |                       |  |  |  |

| Width: $w$                                                                                                |                    |                      |                       |  |  |  |

| Spacing: s                                                                                                |                    | T                    |                       |  |  |  |

| Thickness: t                                                                                              |                    | T                    |                       |  |  |  |

| Interlayer oxide height: h                                                                                |                    | T                    |                       |  |  |  |

| Characteristics Per Unit Length                                                                           |                    |                      |                       |  |  |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	extstyle w}$                                     |                    |                      |                       |  |  |  |

| Fringing capacitance per unit length: $C_{\!\scriptscriptstyle { m w}\!f}$                                |                    |                      | +                     |  |  |  |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  |                    |                      | 1                     |  |  |  |

| Total wire capacitance per unit length: $C_w$                                                             |                    | 1                    | '                     |  |  |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          |                    |                      |                       |  |  |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                    |                      |                       |  |  |  |

| Crosstalk noise                                                                                           |                    |                      |                       |  |  |  |

| Table 4.16 Influence of scaling on interconnect characteris  Parameter Sensitivity Reduced                |             |           |                       |  |

|-----------------------------------------------------------------------------------------------------------|-------------|-----------|-----------------------|--|

| Parameter                                                                                                 | Sensitivity | Thickness | Constant<br>Thickness |  |

| Scaling P                                                                                                 | arameters   |           |                       |  |

| Width: w                                                                                                  |             |           | 1/ <i>S</i>           |  |

| Spacing: s                                                                                                |             |           | 1/S                   |  |

| Thickness: t                                                                                              |             | 1/S       | 1                     |  |

| Interlayer oxide height: <i>h</i>                                                                         |             |           | 1/ <i>S</i>           |  |

| Characteristics Per Unit Length                                                                           |             |           |                       |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	ext{w}}$                                         |             | ,         | '                     |  |

| Fringing capacitance per unit length: $C_{\it wf}$                                                        |             |           | -                     |  |

| Parallel plate capacitance per unit length: $C_{wp}$                                                      |             | -         | +                     |  |

| Total wire capacitance per unit length: $C_w$                                                             |             | -         | -                     |  |

| Unrepeated RC constant per unit length: $t_{xuv}$                                                         |             |           |                       |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |             |           |                       |  |

| Crosstalk noise                                                                                           |             | 1         | 1                     |  |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                |                      |                       |

|-----------------------------------------------------------------------------------------------------------|----------------|----------------------|-----------------------|

| Parameter                                                                                                 | Sensitivity    | Reduced<br>Thickness | Constant<br>Thickness |

| Scaling Pa                                                                                                | arameters      |                      | •                     |

| Width: ω                                                                                                  |                | 1                    | /S                    |

| Spacing: s                                                                                                |                | 1                    | /S                    |

| Thickness: t                                                                                              |                | 1/S                  | 1                     |

| Interlayer oxide height: h                                                                                |                | 1                    | /S                    |

| Characteristics Per Unit Length                                                                           |                |                      |                       |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	ext{w}}$                                         | $\frac{1}{wt}$ | $S^2$                | S                     |

| Fringing capacitance per unit length: $C_{\it wf}$                                                        |                | 1                    | +                     |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  |                | 1                    | 1                     |

| Total wire capacitance per unit length: $C_w$                                                             |                | +                    | 1                     |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          |                |                      |                       |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                |                      |                       |

| Crosstalk noise                                                                                           |                |                      |                       |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                |                      |                       |  |

|-----------------------------------------------------------------------------------------------------------|----------------|----------------------|-----------------------|--|

| Parameter                                                                                                 | Sensitivity    | Reduced<br>Thickness | Constant<br>Thickness |  |

| Scaling P                                                                                                 | arameters      |                      | •                     |  |

| Width: w                                                                                                  |                | 1                    | 1/S                   |  |

| Spacing: s                                                                                                |                | 1                    | 1/S                   |  |

| Thickness: t                                                                                              |                | 1/S                  | 1                     |  |

| Interlayer oxide height: h                                                                                |                | 1                    | /S                    |  |

| Characteristics Per Unit Length                                                                           |                |                      |                       |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	extsf{w}}$                                       | $\frac{1}{wt}$ | $S^2$                | S                     |  |

| Fringing capacitance per unit length: $C_{\!w\!f}$                                                        | <u>t</u><br>s  | 1                    | S                     |  |

| Parallel plate capacitance per unit length: $C_{\!w\!p}$                                                  |                |                      | +                     |  |

| Total wire capacitance per unit length: $C_{\it w}$                                                       |                | 1                    | 1                     |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          |                |                      |                       |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                |                      |                       |  |

| Crosstalk noise                                                                                           |                |                      |                       |  |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                |                      |                       |  |

|-----------------------------------------------------------------------------------------------------------|----------------|----------------------|-----------------------|--|

| Parameter                                                                                                 | Sensitivity    | Reduced<br>Thickness | Constant<br>Thickness |  |

| Scaling Pa                                                                                                | arameters      |                      | •                     |  |

| Width: w                                                                                                  |                | 1                    | /S                    |  |

| Spacing: s                                                                                                |                | 1                    | /S                    |  |

| Thickness: t                                                                                              |                | 1/S                  | 1                     |  |

| Interlayer oxide height: h                                                                                |                | 1                    | /S                    |  |

| Characteristics Per Unit Length                                                                           |                |                      |                       |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle w}$                                               | $\frac{1}{wt}$ | $S^2$                | S                     |  |

| Fringing capacitance per unit length: $C_{\!w\!f}$                                                        | $\frac{t}{s}$  | 1                    | S                     |  |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  | $\frac{w}{b}$  | 1                    | 1                     |  |

| Total wire capacitance per unit length: $C_{\!w}$                                                         |                | 1                    | '                     |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          |                |                      |                       |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                |                      |                       |  |

| Crosstalk noise                                                                                           |                | ,                    |                       |  |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                     |                      |                       |  |

|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------|-----------------------|--|

| Parameter                                                                                                 | Sensitivity         | Reduced<br>Thickness | Constant<br>Thickness |  |

| Scaling Pa                                                                                                | rameters            |                      |                       |  |

| Width: w                                                                                                  |                     | 1/S                  |                       |  |

| Spacing: s                                                                                                |                     | 1.                   | /S                    |  |

| Thickness: t                                                                                              |                     | 1/S                  | 1                     |  |

| Interlayer oxide height: h                                                                                |                     | 1.                   | /S                    |  |

| Characteristics Per Unit Length                                                                           |                     |                      |                       |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	exttt{w}}$                                       | $\frac{1}{wt}$      | $S^2$                | S                     |  |

| Fringing capacitance per unit length: $C_{wf}$                                                            | <u>t</u><br>s       | 1                    | S                     |  |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  | $\frac{w}{b}$       | 1                    | 1                     |  |

| Total wire capacitance per unit length: $C_w$                                                             | $C_{wf}$ + $C_{wp}$ | 1                    | between 1, S          |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          |                     |                      |                       |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                     |                      |                       |  |

| Crosstalk noise                                                                                           |                     | 1                    | 1                     |  |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                     |                      |                       |  |

|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------|-----------------------|--|

| Parameter                                                                                                 | Sensitivity         | Reduced<br>Thickness | Constant<br>Thickness |  |

| Scaling Pa                                                                                                | rameters            |                      |                       |  |

| Width: w                                                                                                  |                     | 1                    | /S                    |  |

| Spacing: s                                                                                                |                     | 1                    | /S                    |  |

| Thickness: t                                                                                              |                     | 1/S                  | 1                     |  |

| Interlayer oxide height: $b$                                                                              |                     | 1                    | /S                    |  |

| Characteristics Per Unit Length                                                                           |                     |                      |                       |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	extstyle w}$                                     | $\frac{1}{wt}$      | $S^2$                | S                     |  |

| Fringing capacitance per unit length: $C_{w\!f}$                                                          | <u>t</u><br>s       | 1                    | S                     |  |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  | $\frac{w}{b}$       | 1                    | 1                     |  |

| Total wire capacitance per unit length: $C_{\it w}$                                                       | $C_{wf}$ + $C_{wp}$ | 1                    | between 1, S          |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          | $R_wC_w$            | S <sup>2</sup>       | between $S$ , $S^2$   |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) |                     |                      |                       |  |

| Crosstalk noise                                                                                           |                     |                      | i                     |  |

| Parameter                                                                                                 | Sensitivity         | Reduced        | characteristics Reduced Constant |  |

|-----------------------------------------------------------------------------------------------------------|---------------------|----------------|----------------------------------|--|

| raidilietei                                                                                               | Sensitivity         | Thickness      | Thickness                        |  |

| Scaling Pa                                                                                                | arameters           |                |                                  |  |

| Width: $w$                                                                                                |                     | :              | 1/S                              |  |

| Spacing: s                                                                                                |                     | :              | 1/ <i>S</i>                      |  |

| Thickness: t                                                                                              |                     | 1/S            | 1                                |  |

| Interlayer oxide height: $b$                                                                              |                     | :              | 1/ <i>S</i>                      |  |

| Characteristics Per Unit Length                                                                           |                     |                |                                  |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	ext{w}}$                                         | $\frac{1}{wt}$      | S <sup>2</sup> | S                                |  |

| Fringing capacitance per unit length: $C_{w\!f}$                                                          | $\frac{t}{s}$       | 1              | S                                |  |

| Parallel plate capacitance per unit length: $C_{\it wp}$                                                  | $\frac{w}{b}$       | 1              | 1                                |  |

| Total wire capacitance per unit length: $C_w$                                                             | $C_{wf}$ + $C_{wp}$ | 1              | between 1, S                     |  |

| Unrepeated RC constant per unit length: $t_{ww}$                                                          | $R_wC_w$            | $S^2$          | between S,<br>S <sup>2</sup>     |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) | $\sqrt{RCR_wC_w}$   | $\sqrt{S}$     | between 1, $\sqrt{S}$            |  |

| Crosstalk noise                                                                                           |                     |                | 1                                |  |

| Table 4.16 Influence of scaling on interconnect characteristics                                           |                     |                      |                              |  |

|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------------------|--|

| Parameter                                                                                                 | Sensitivity         | Reduced<br>Thickness | Constant<br>Thickness        |  |

| Scaling Pa                                                                                                | rameters            |                      | •                            |  |

| Width: $w$                                                                                                |                     | 1                    | 1/ <i>S</i>                  |  |

| Spacing: s                                                                                                |                     | 1                    | /S                           |  |

| Thickness: t                                                                                              |                     | 1/S                  | 1                            |  |

| Interlayer oxide height: h                                                                                |                     | 1                    | /S                           |  |

| Characteristics Per Unit Length                                                                           |                     |                      |                              |  |

| Wire resistance per unit length: $R_{\scriptscriptstyle 	exttt{w}}$                                       | 1<br>wt             | $S^2$                | S                            |  |

| Fringing capacitance per unit length: $C_{\it wf}$                                                        | <u>t</u><br>s       | 1                    | S                            |  |

| Parallel plate capacitance per unit length: $C_{w\!p}$                                                    | $\frac{w}{h}$       | 1                    | 1                            |  |

| Total wire capacitance per unit length: $C_{w}$                                                           | $C_{wf}$ + $C_{wp}$ | 1                    | between 1, S                 |  |

| Unrepeated RC constant per unit length: $t_{wu}$                                                          | $R_wC_w$            | S <sup>2</sup>       | between S,<br>S <sup>2</sup> |  |

| Repeated wire RC delay per unit length: $t_{wr}$ (assuming constant field scaling of gates in Table 4.15) | $\sqrt{RCR_wC_w}$   | <b>√</b> S           | between 1, $\sqrt{S}$        |  |

| Crosstalk noise                                                                                           | <u>t</u><br>s       | 1                    | S                            |  |

| Parameter                             | Sensitivity      | Reduced<br>Thickness | Constant<br>Thickness |  |  |

|---------------------------------------|------------------|----------------------|-----------------------|--|--|

| Sc                                    | aling Parameters |                      |                       |  |  |

| Width: ω                              |                  |                      | 1/S                   |  |  |

| Spacing: s                            |                  |                      | 1/ <i>S</i>           |  |  |

| Thickness: t                          |                  | 1/S                  | 1                     |  |  |

| Interlayer oxide height: <i>b</i>     |                  | 1/S                  |                       |  |  |

| Local/Scaled Interconnect Characteris | tics             |                      | •                     |  |  |

| Length: /                             |                  |                      |                       |  |  |

| Unrepeated wire RC delay              |                  |                      |                       |  |  |

| Repeated wire delay                   |                  |                      | -                     |  |  |

| Global Interconnect Characteristics   |                  |                      | 1                     |  |  |

| Length: /                             |                  |                      |                       |  |  |

| Unrepeated wire RC delay              |                  |                      |                       |  |  |

| Repeated wire delay                   |                  | 1                    | +                     |  |  |

| Parameter                              | Sensitivity     | Reduced<br>Thickness | Constant<br>Thickness |  |  |

|----------------------------------------|-----------------|----------------------|-----------------------|--|--|

| Sca                                    | ling Parameters |                      |                       |  |  |

| Width: $w$                             |                 |                      | 1/ <i>S</i>           |  |  |

| Spacing: s                             |                 |                      | 1/ <i>S</i>           |  |  |

| Thickness: t                           |                 | 1/S                  | 1                     |  |  |

| Interlayer oxide height: b             |                 |                      | 1/S                   |  |  |

| Local/Scaled Interconnect Characterist | ics             |                      | •                     |  |  |

| Length: /                              |                 | 1/S                  |                       |  |  |

| Unrepeated wire RC delay               |                 | '                    | 1                     |  |  |

| Repeated wire delay                    |                 | -                    |                       |  |  |

| Global Interconnect Characteristics    |                 |                      | -                     |  |  |

| Length: /                              |                 |                      |                       |  |  |

| Unrepeated wire RC delay               |                 |                      |                       |  |  |

| Repeated wire delay                    |                 | 1                    | +                     |  |  |

| Parameter                             | Sensitivity      | Reduced<br>Thickness | Constant<br>Thickness |  |  |

|---------------------------------------|------------------|----------------------|-----------------------|--|--|

| Sc                                    | aling Parameters |                      |                       |  |  |

| Width: ω                              |                  |                      | 1/ <i>S</i>           |  |  |

| Spacing: s                            |                  |                      | 1/ <i>S</i>           |  |  |

| Thickness: t                          |                  | 1/S                  | 1                     |  |  |

| Interlayer oxide height: b            |                  |                      | 1/S                   |  |  |

| Local/Scaled Interconnect Characteris | tics             |                      |                       |  |  |

| Length: /                             |                  | 1/S                  |                       |  |  |

| Unrepeated wire RC delay              | $l^2t_{wu}$      | 1                    | between 1/S, 1        |  |  |

| Repeated wire delay                   |                  |                      |                       |  |  |

| Global Interconnect Characteristics   | !                |                      |                       |  |  |

| Length: /                             |                  |                      |                       |  |  |

| Unrepeated wire RC delay              |                  | •                    |                       |  |  |

| Repeated wire delay                   |                  | -                    | +                     |  |  |

| Parameter                           | Sensitivity       | Reduced<br>Thickness | Constant<br>Thickness        |  |  |

|-------------------------------------|-------------------|----------------------|------------------------------|--|--|

| S                                   | caling Parameters |                      |                              |  |  |

| Width: w                            |                   |                      | 1/ <i>S</i>                  |  |  |

| Spacing: s                          |                   |                      | 1/ <i>S</i>                  |  |  |

| Thickness: t                        |                   | 1/S                  | 1                            |  |  |

| Interlayer oxide height: h          |                   |                      | 1/S                          |  |  |

| Local/Scaled Interconnect Character | istics            |                      | •                            |  |  |

| Length: /                           |                   |                      | 1/S                          |  |  |

| Unrepeated wire RC delay            | $l^2 t_{wu}$      | 1                    | between 1/S, 1               |  |  |

| Repeated wire delay                 | $lt_{wr}$         | $\sqrt{1/S}$         | between $1/S$ , $\sqrt{1/s}$ |  |  |

| Global Interconnect Characteristics |                   |                      |                              |  |  |

| Length: /                           |                   |                      |                              |  |  |

| Unrepeated wire RC delay            |                   |                      |                              |  |  |

| Repeated wire delay                 |                   | ·                    | +                            |  |  |

| Parameter                            | Sensitivity       | Reduced<br>Thickness | Constant<br>Thickness        |  |  |

|--------------------------------------|-------------------|----------------------|------------------------------|--|--|

| S                                    | caling Parameters |                      |                              |  |  |

| Width: w                             |                   |                      | 1/ <i>S</i>                  |  |  |

| Spacing: s                           |                   |                      | 1/ <i>S</i>                  |  |  |

| Thickness: t                         |                   | 1/S                  | 1                            |  |  |

| Interlayer oxide height: h           |                   |                      | 1/S                          |  |  |

| Local/Scaled Interconnect Characteri | istics            |                      | •                            |  |  |

| Length: /                            |                   |                      | 1/S                          |  |  |

| Unrepeated wire RC delay             | $l^2 t_{wu}$      | 1                    | between 1/S, 1               |  |  |

| Repeated wire delay                  | lt <sub>wr</sub>  | $\sqrt{1/S}$         | between $1/S$ , $\sqrt{1/s}$ |  |  |

| Global Interconnect Characteristics  |                   |                      |                              |  |  |

| Length: /                            |                   | $D_{\epsilon}$       |                              |  |  |

| Unrepeated wire RC delay             |                   |                      |                              |  |  |

| Repeated wire delay                  |                   | ·                    | +                            |  |  |

| Parameter                           | Sensitivity        | Reduced<br>Thickness | Constant<br>Thickness         |  |  |

|-------------------------------------|--------------------|----------------------|-------------------------------|--|--|

| :                                   | Scaling Parameters |                      |                               |  |  |

| Width: w                            |                    |                      | 1/ <i>S</i>                   |  |  |

| Spacing: s                          |                    |                      | 1/ <i>S</i>                   |  |  |

| Thickness: t                        |                    | 1/S                  | 1                             |  |  |

| Interlayer oxide height: b          |                    |                      | 1/S                           |  |  |

| Local/Scaled Interconnect Characte  | ristics            |                      | ·                             |  |  |

| Length: /                           |                    | 1/S                  |                               |  |  |

| Unrepeated wire RC delay            | $l^2t_{wu}$        | 1                    | between 1/S, 1                |  |  |

| Repeated wire delay                 | $lt_{wr}$          | $\sqrt{1/S}$         | between $1/S$ , $\sqrt{1/S}$  |  |  |

| Global Interconnect Characteristics |                    |                      |                               |  |  |

| Length: /                           |                    |                      | $D_{\epsilon}$                |  |  |

| Unrepeated wire RC delay            | $l^2t_{wu}$        | $S^2D_c^2$           | between $SD_c^2$ , $S^2D_c^2$ |  |  |

| Repeated wire delay                 |                    | 1                    | -                             |  |  |

| Parameter                            | Sensitivity       |                | Constant<br>Thickness         |  |  |

|--------------------------------------|-------------------|----------------|-------------------------------|--|--|

| S                                    | caling Parameters |                | -                             |  |  |

| Width: w                             |                   |                | 1/ <i>S</i>                   |  |  |

| Spacing: s                           |                   |                | 1/ <i>S</i>                   |  |  |

| Thickness: t                         |                   | 1/S            | 1                             |  |  |

| Interlayer oxide height: h           |                   |                | 1/S                           |  |  |

| Local/Scaled Interconnect Characteri | stics             |                | •                             |  |  |

| Length: /                            |                   | 1/S            |                               |  |  |

| Unrepeated wire RC delay             | $l^2t_{wu}$       | 1              | between $1/S$ , 1             |  |  |

| Repeated wire delay                  | $lt_{wr}$         | $\sqrt{1/S}$   | between $1/S$ , $\sqrt{1/S}$  |  |  |

| Global Interconnect Characteristics  |                   |                |                               |  |  |

| Length: /                            |                   |                | $D_{\epsilon}$                |  |  |

| Unrepeated wire RC delay             | $l^2t_{wu}$       | $S^2D_c^2$     | between $SD_c^2$ , $S^2D_c^2$ |  |  |

| Repeated wire delay                  | lt <sub>wr</sub>  | $D_c \sqrt{S}$ | between $D$ $D_c \sqrt{S}$    |  |  |

### Observations

- · Capacitance per micron is remaining constant

- About 0.2 fF/μm

- Roughly 1/10 of gate capacitance

- · Local wires are getting faster

- Not quite tracking transistor improvement

- But not a major problem

- Global wires are getting slower

- No longer possible to cross chip in one cycle

### ITRS

- Semiconductor Industry Association forecast

- Intl. Technology Roadmap for Semiconductors

| Table 4.17 Predictions from the 2002 ITRS |         |         |         |         |         |         |  |

|-------------------------------------------|---------|---------|---------|---------|---------|---------|--|

| Year                                      | 2001    | 2004    | 2007    | 2010    | 2013    | 2016    |  |

| Feature size (nm)                         | 130     | 90      | 65      | 45      | 32      | 22      |  |

| $V_{DD}\left(\mathbf{V}\right)$           | 1.1-1.2 | 1-1.2   | 0.7-1.1 | 0.6-1.0 | 0.5-0.9 | 0.4-0.9 |  |

| Millions of transistors/die               | 193     | 385     | 773     | 1564    | 3092    | 6184    |  |

| Wiring levels                             | 8-10    | 9–13    | 10–14   | 10–14   | 11–15   | 11-15   |  |

| Intermediate wire pitch (nm)              | 450     | 275     | 195     | 135     | 95      | 65      |  |

| Interconnect dielectric constant          | 3–3.6   | 2.6-3.1 | 2.3-2.7 | 2.1     | 1.9     | 1.8     |  |

| I/O signals                               | 1024    | 1024    | 1024    | 1280    | 1408    | 1472    |  |

| Clock rate (MHz)                          | 1684    | 3990    | 6739    | 11511   | 19348   | 28751   |  |

| FO4 delays/cycle                          | 13.7    | 8.4     | 6.8     | 5.8     | 4.8     | 4.7     |  |

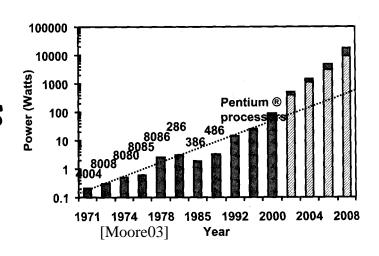

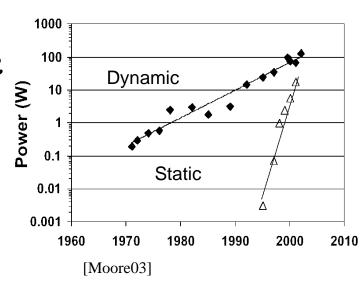

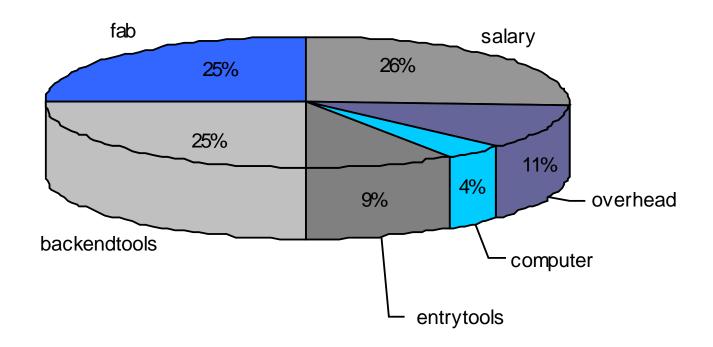

| Maximum power (W)                         | 130     | 160     | 190     | 218     | 251     | 288     |  |