#### Prospect and Plan for IRS3B Readout

- 1. Progress on Key Performance Parameters

- 2. Understanding limitations during LEPS operation

- 3. Carrier02 Rev. C (with O-E-M improvements)

- 4. Pre-production tasks/schedule

Toru Iijima

Aug. 21, 2013 KEKB Steering Committee report

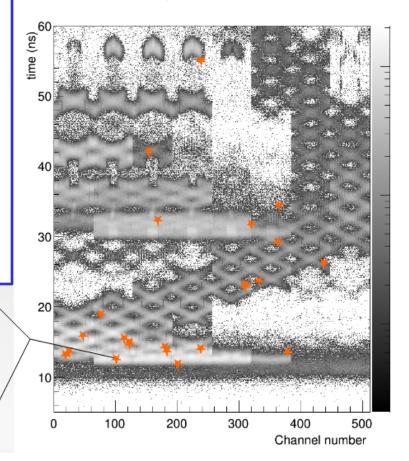

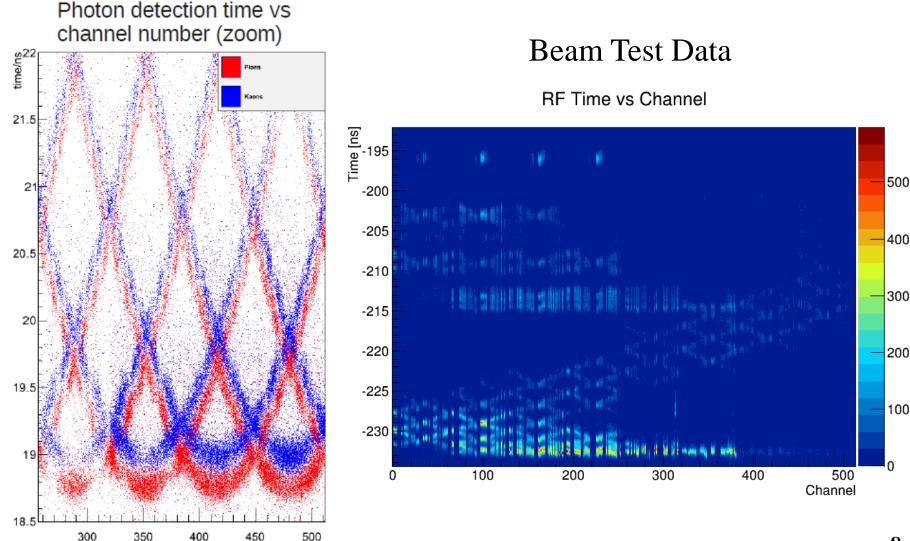

Beamtest Experiment 2 Run 568 Event 1

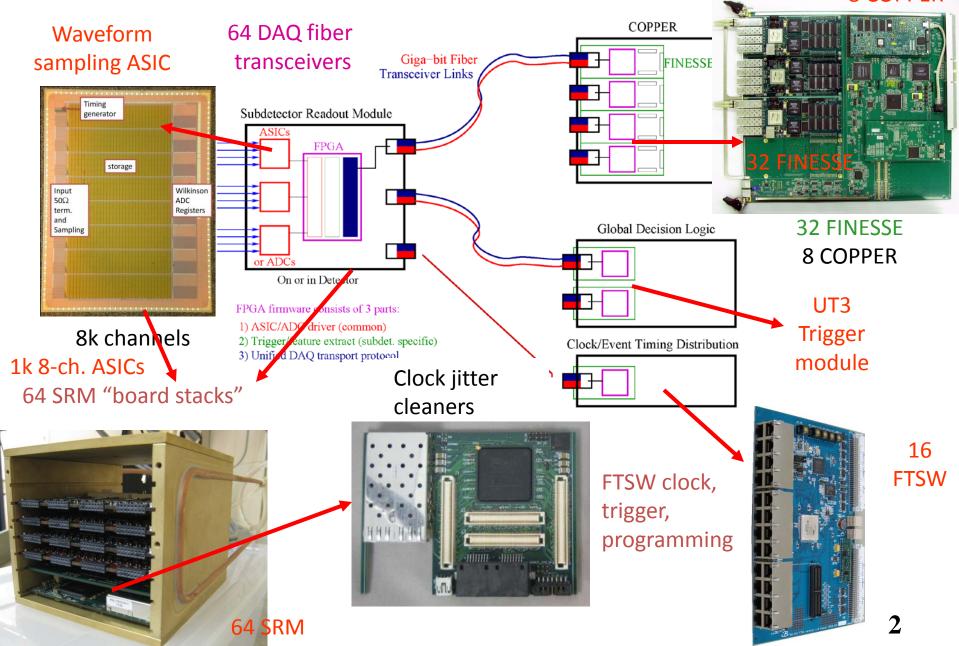

### IRS3B-based Readout Overview 8 COPPER

### **Executive Summary**

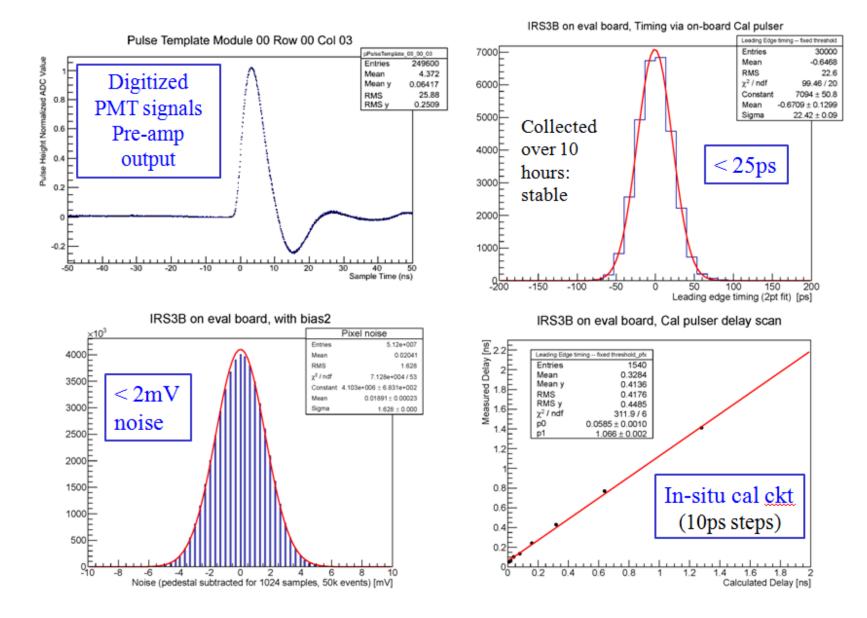

- After commissioning/learning period, now obtaining electronics resolutions commensurate with stated minimum requirements (<100ps timing)

- Still room to improve:

- Processing: timebase cal, leading edge timing extraction

Board improvements: sampling timebase, gain, risetime

- Rev. C Carrier boards [improved mechanics, amplifiers, signal coupling] being assembled, testing soon

- IRS3C [extended dynamic range] due this week

- Details in subsequent slides

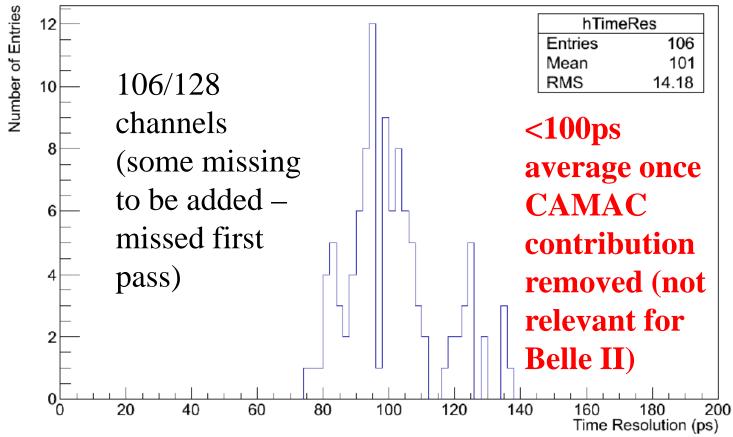

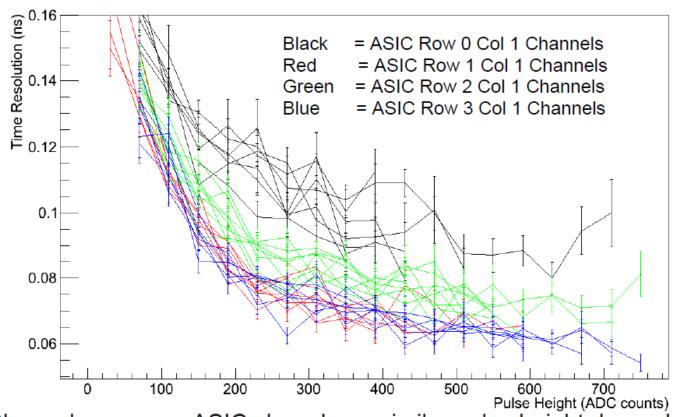

# Board Stack #37 <u>single photon</u> timing, no ADC cuts, no modifications from LEPS configuration

Laser Data Channel Time Resolutions

- Overall average time resolution is 101 +/- 14 ps

- Need to understand large variation in time resolution across channels

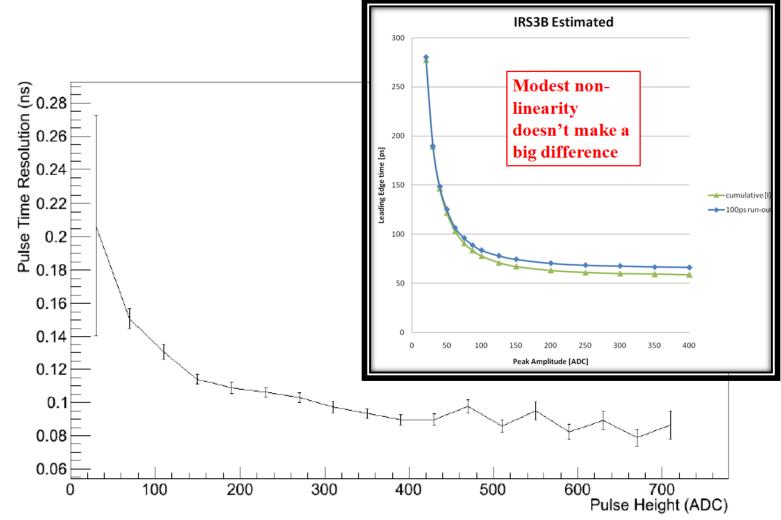

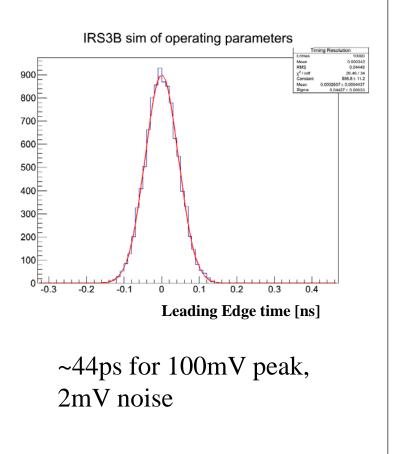

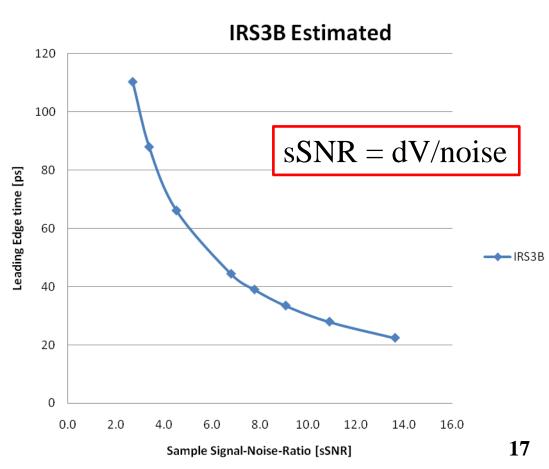

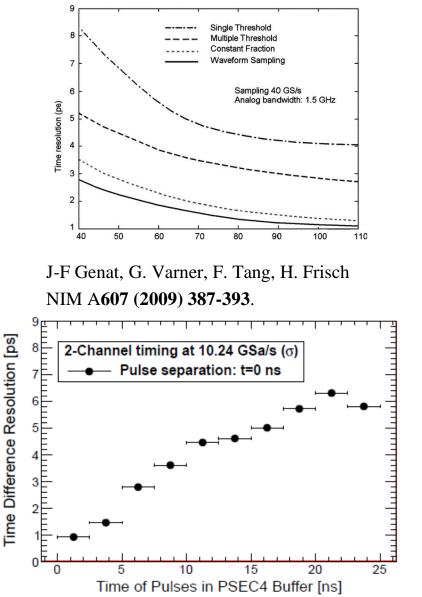

### As understood from simulation

- Time resolution clearly depends on pulse neight

- To a large extent, channel time resolution will depend on pulse height distribution

# Channels within same ASIC similar – common timing/timebase issue

Channels on same ASIC share have similar pulse height dependence for time resolution

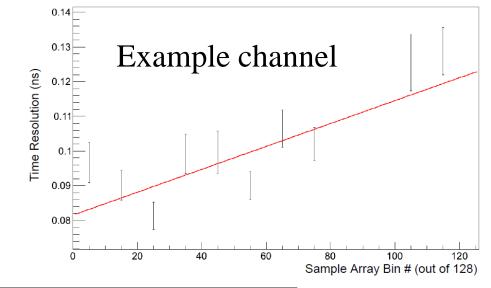

#### If dominated by DAC/VadjN jitter, should see clear dependence...

#### And it is clearly observed

Probably a combination of jitter (noise on VadjN) and coarseness of DAC [under study]

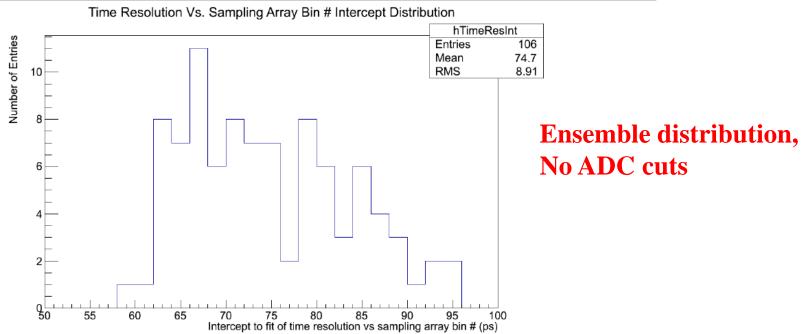

- Plot distribution of intercepts from linear fit to time resolution vs. sampling array bin # plot

- Represents time resolution if there was no degradation along sampling array

#### Pedagogical slides about timing...

• Space-time correlations

Channel number

#### About LEPS timing current status... (work in progress)

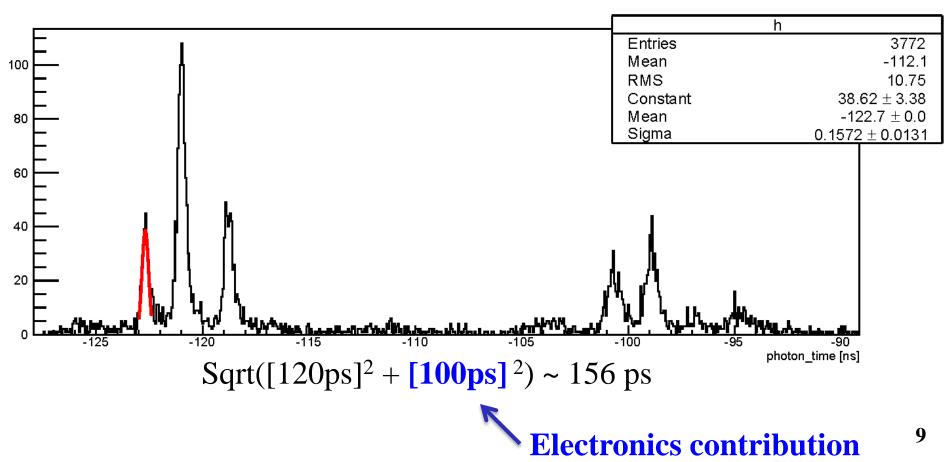

• For large amplitude, corresponding to the tight cuts applied, and assuming ("120ps" width)...

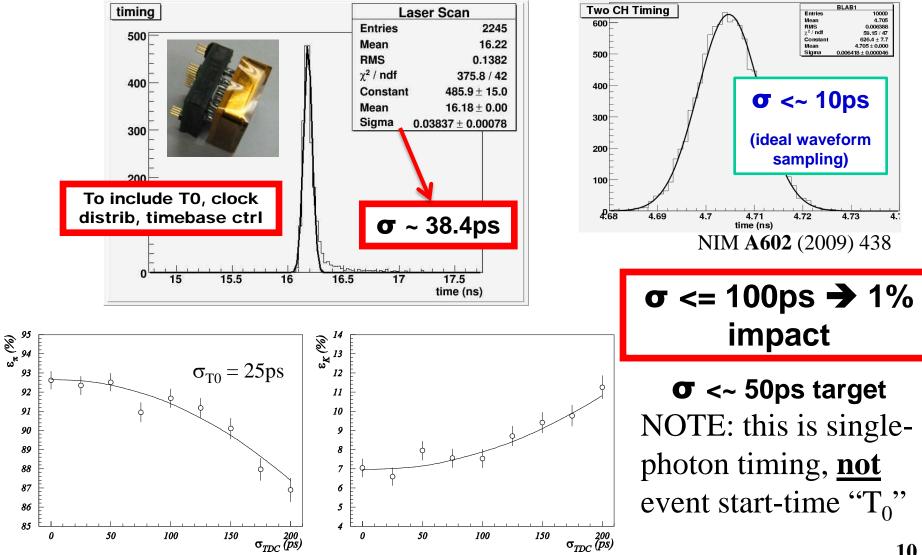

#### Performance Requirements (TOP) • Single photon timing for MCP-PMTs

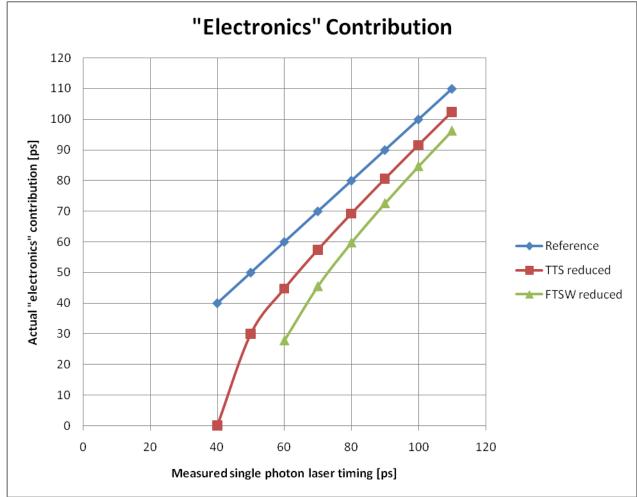

#### **Electronics contribution**

• 100ps is min. required for Key Performance Parameters (50ps target)

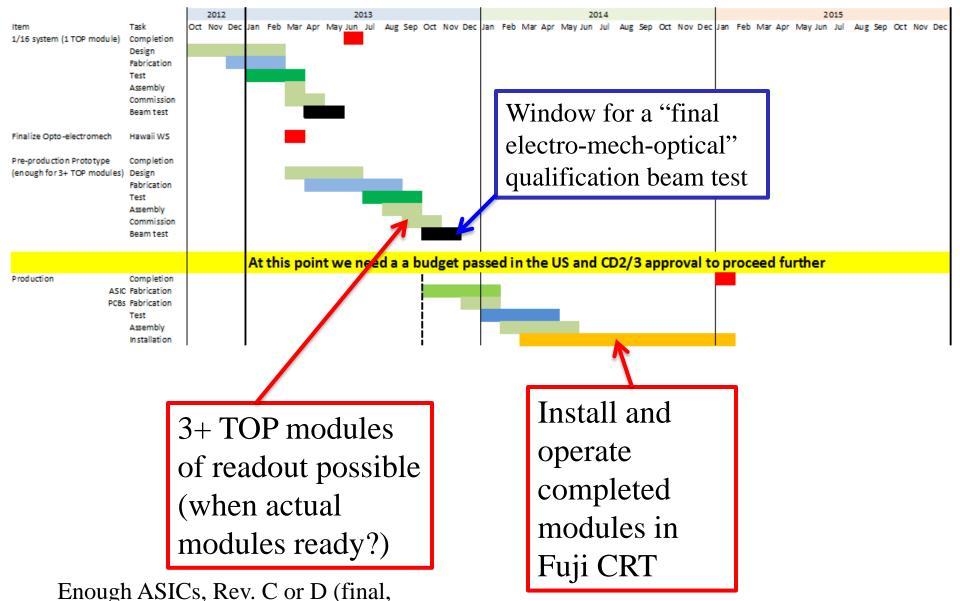

#### **TOP Electronics Production Schedule**

dual-stage amp), SCROD Rev. C (?)

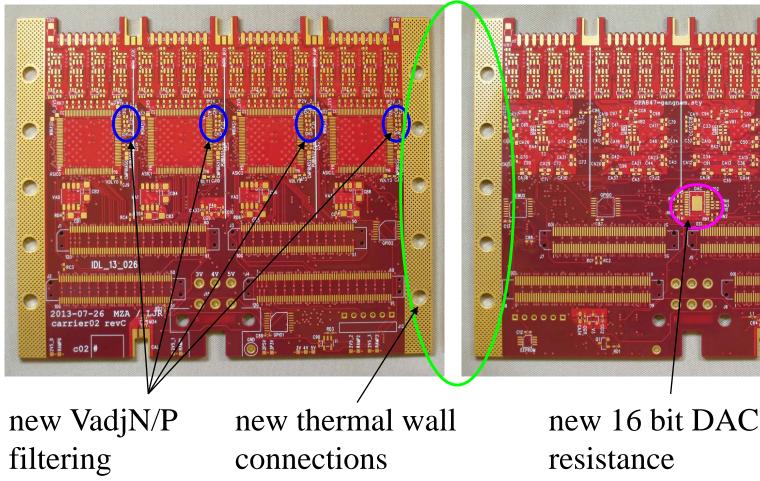

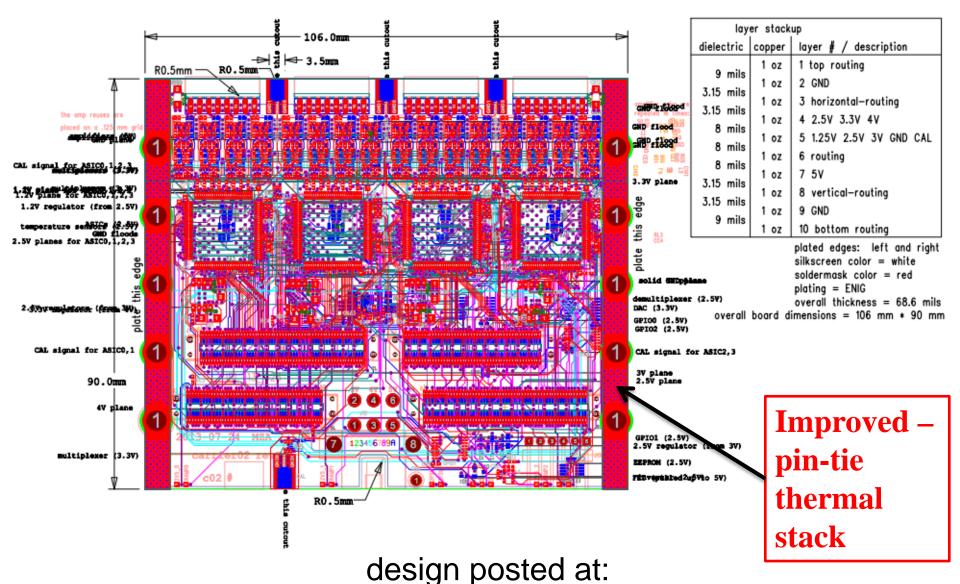

### carrier02 revC improvements

new 16 bit DAC with series resistance

•received PCBs last week

•assembly to begin imminently

•will have assembled boards by end of August

### Status and Prospects

• Have achieved Key Performance Parameters over entire IRS3B-based readout module used in beam test; this is only minimum, <=50ps looks achievable

•Will fabricate/populate Carrier02 [IRS3B limited] so can have spares and distribute for testing elsewhere – improved thermo-mechanics

- IRS3C drop-in for IRS3B [extended dynamic range]

- Demonstrate true timing limits

### Backup

#### Development Timeline (next steps) Dates Milestone(s) Hardware

< Spring '11

Prototyping

Summer '11 – Winter 12

FNAL beamtest

Spring '12 – Winter 12 Semi-infinite reviews

Spring '13 – Summer 13

LEPS beamtest

v.1 RT recon

Autumn '13 v. 3 IRS3C/IRSX

FINv2, final boardstack 16

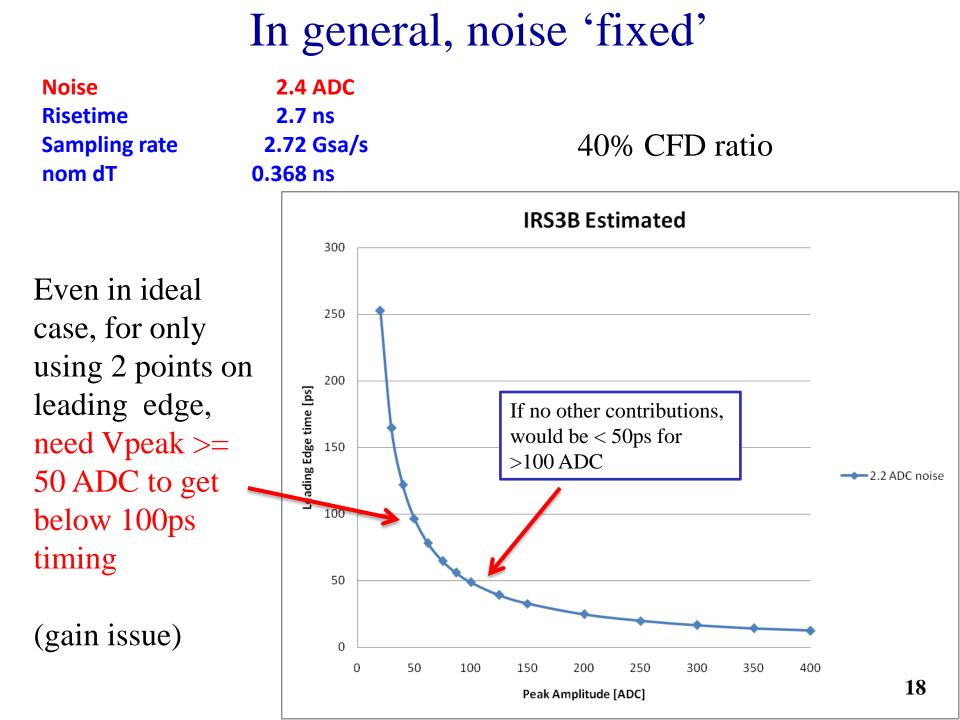

#### Comparison IRS3B "toy" Monte Carlo

| Vpeak         | <b>100 ADC</b>    |

|---------------|-------------------|

| Risetime      | 2.7 ns            |

| Sampling rate | 2.72 Gsa/s        |

| nom dT        | 0.368 ns          |

| nom dV        | 13.617 ADC/sample |

|               |                   |

40% CFD ratio:

Applied between 2 points on leading edge that bracket this transition

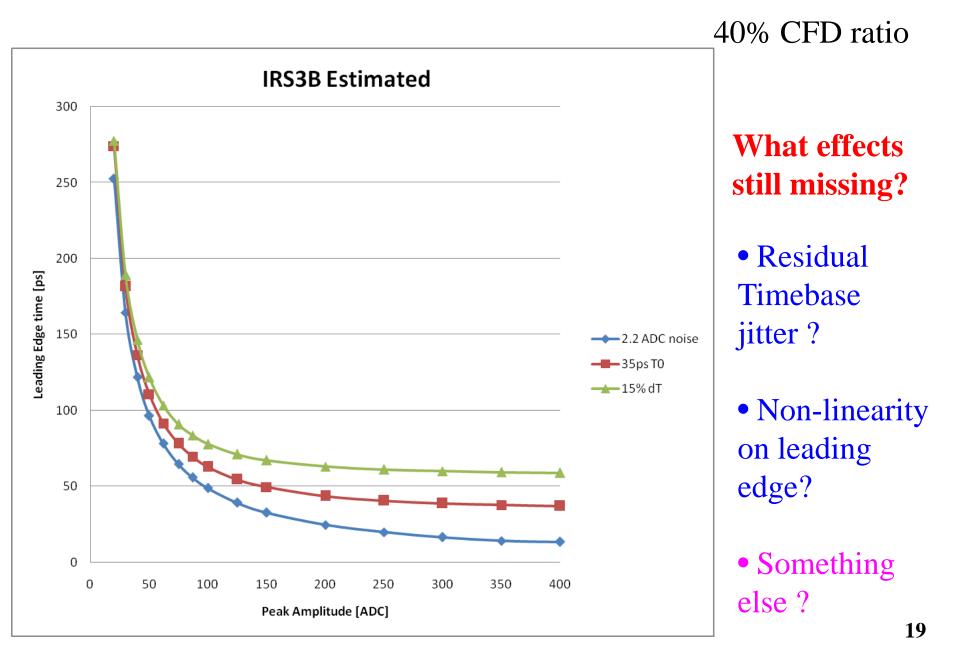

#### Adding in realistic degradations

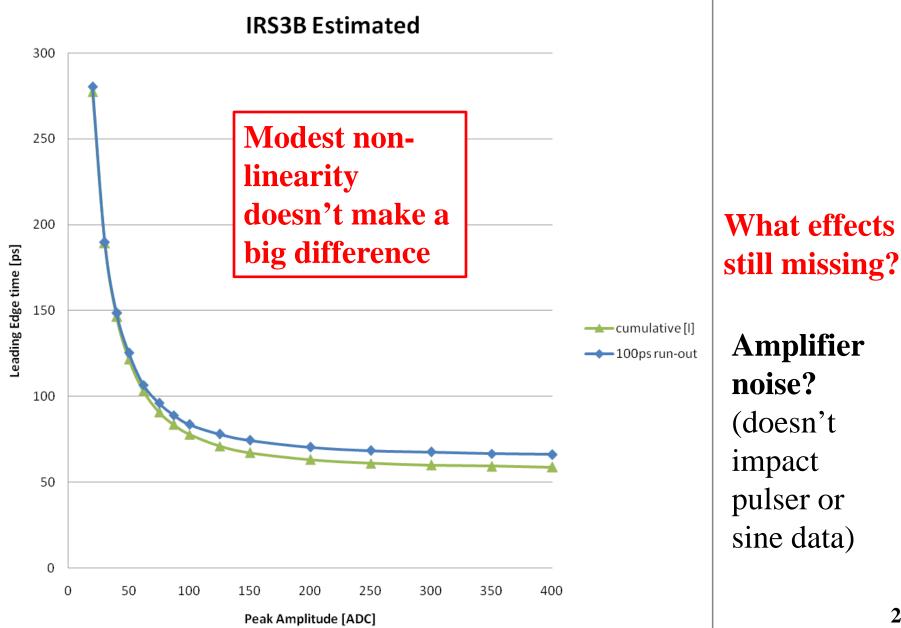

#### Adding in realistic degradations (II)

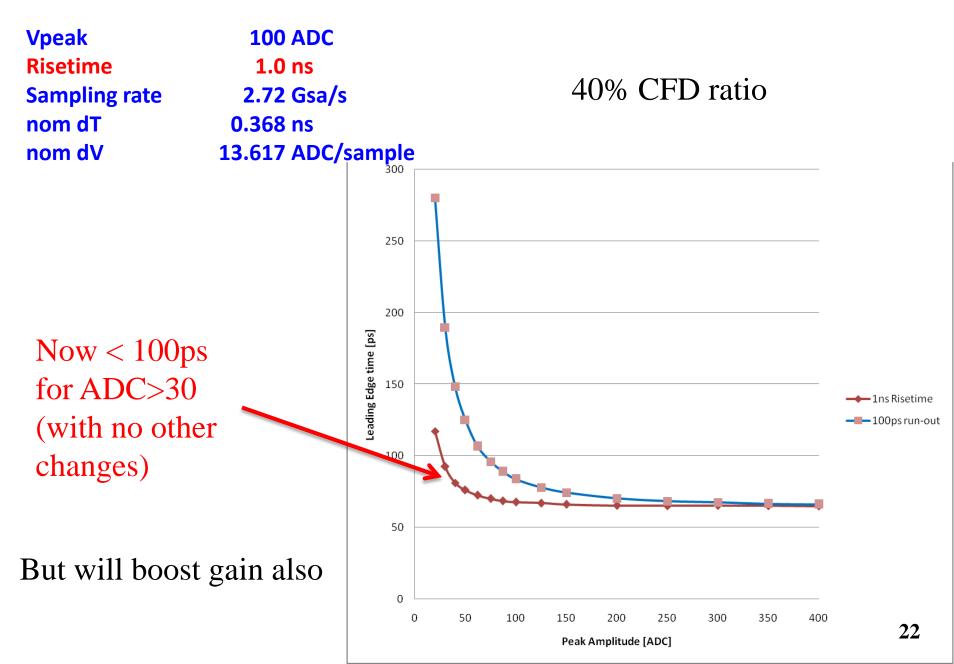

### Ways to improve (short-term)

- 1. Increase gain (straightforward)

- 2. Add Voltage Regulator to amplifier power

- 3. Increase risetime

- 4. Add better VdlyN, VdlyP filtering (reduce timebase filter)

All these to be improved on Carrier02 Thermo-mech prototype (boards have been fabricated, being assembled)

Final mechanics after tests with new HV, front/PMT interface (final board-stack w/IRSX)

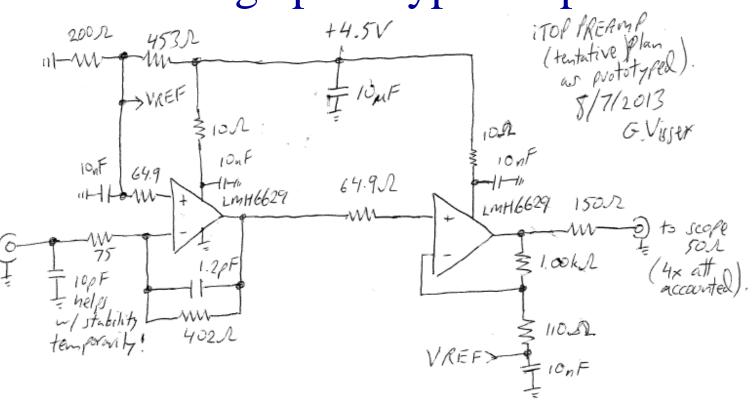

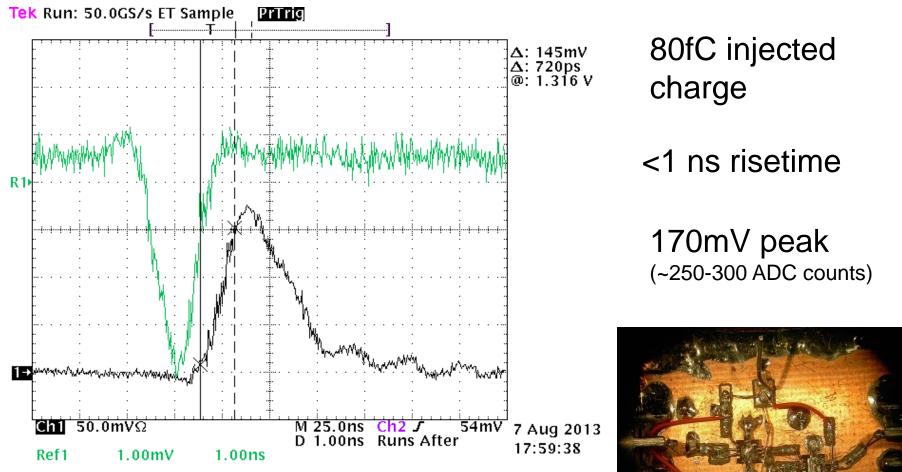

#### One example: improved Risetime

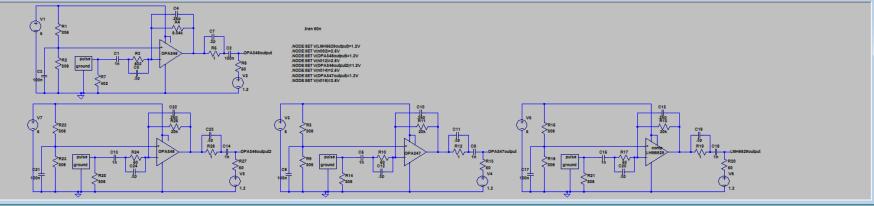

### Improvements to carrier02

- $\sqrt{\text{Will populate with improved amplifiers}}$

- $\sqrt{\text{add series resistor and capacitors to VadjN/VadjP} (10 Ohm+200pF+47nF+2uF})$

- $\sqrt{\text{exchange SMA connectors for MMCX}}$

- $\sqrt{\text{exchange 12 bit external DAC for 16 bit one in same series}}$

- $\sqrt{\text{re-visit c02 wiring to allow powering entire boardstack}}$  with just one cable

- $\sqrt{\text{extend width of boards and add holes for new thermal wall structure concept}}$

- $\sqrt{\text{swap ASIC regulator for one with a shutdown feature}}$ full list at http://www.phys.hawaii.edu/~mza/PCB/iTOP/boardstack-v3.html

#### Layout of carrier02 revC

http://www.phys.hawaii.edu/~mza/PCB/iTOP/carriers/index.html

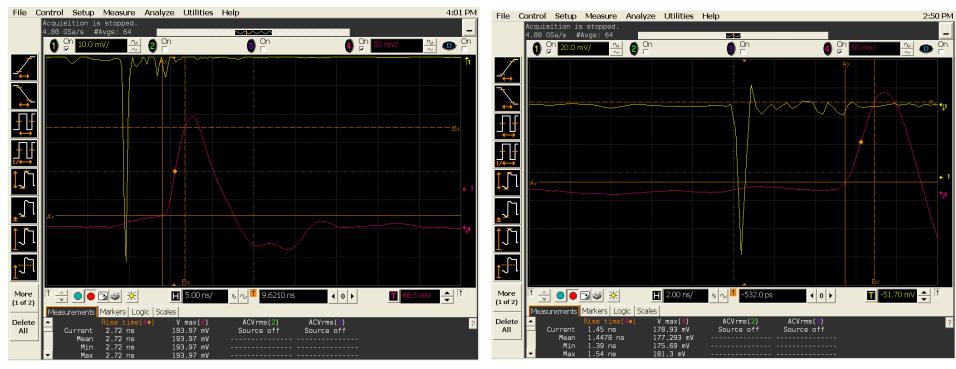

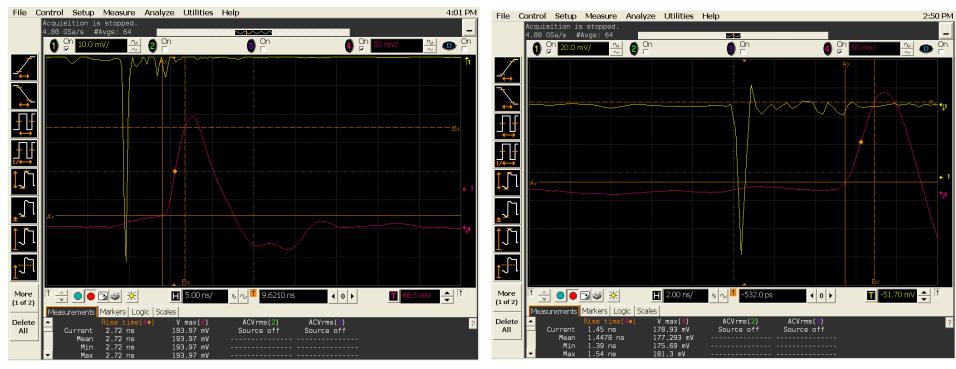

#### 2-stage prototype Amp

2.72 ns risetime

1.45 ns risetime

Optimization study ongoing ...

#### 2-stage prototype Amp -- measurements

Some care required to avoid oscillations..

#### For Rev C Carrier02

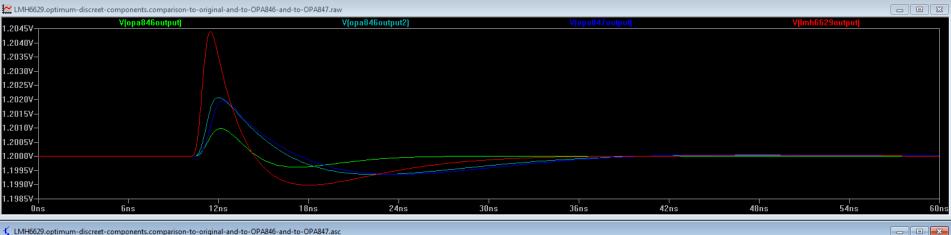

Simulation indicates -- prior to changing layout radically (2x stage design), can already improve amplitude/risetime by switching to LHM6629 (single stage)

Need to confirm stability – will populate first batch with this circuit

#### Optimizing gain, risetime for "drop in" amp

# original circuit (OPA846, 6k feedback)

new circuit (OPA847, 2.4k feedback)

#### 2.72 ns risetime

1.45 ns risetime

Previous measurements...

#### Optimizing gain, risetime for "drop in" amp

# original circuit (OPA846, 6k feedback)

new circuit (OPA847, 2.4k feedback)

#### 2.72 ns risetime

1.45 ns risetime

Optimization study ongoing ...

#### Next steps: IRS3C & IRSX ASICs

( 🔶 ) 🛞 www.phys.hawaii.edu/~idlab/taskAndSchedule/ASIC/IRSX/IRSX\_homepage.html

🔊 Most Visited 🔅 T&S 🔅 Getting Started 🏧 Problem loading page

#### IRS Rev. X [Belle II iTOP (pen)ultimate ASIC]

#### **Design Reference Page**

[counts]

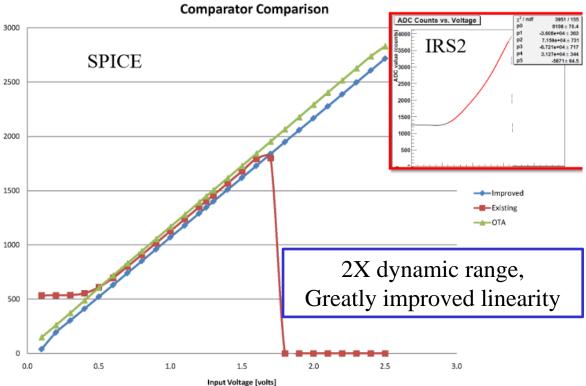

## IRS3C = IRS3B + 2 small changes

(in fab – due imminently)

Predecessor relevant documentation is provided on the IRS3C page and IRS3B page

#### Submission Status Update (30-JUN-2013)

- 1. In order to match funding profile, "1/4" batch of ASICs need to be ordered "soon" (7/29 and 8/19)

- 2. Proposed changes (for discussion):

- 1. Trigger path gain boost (for lower threshold operation)

- 2. Make SSTin LVDS (and point-point from SCROD Rev. B)

- Remove TRGmon to free up pins

- Move to common WL\_CLK (Wilkinson clock), bring in as LVDS, sample phase (2x sampling speed)

Remove Vdly, TST\_out

- No Start, overflow detect needed (just stop counting at desired saturation valu)

- 4. WBias as monitor only? (Analog multiplexer?)

- 5. WR\_ADDR increment set from internal/programmable delay [internal address cloc]

Increment value [3-bit? -- skip ROI?] from SCROD (?)

- Needs reset

- 6. h-GRAPH/TARGET7 extended dynamic range/linearity comparator modifications

- 7. DONE signal to indicate when all conversions are complete (reduce deadtime)

- Charge pump prototype(?)

Exploit lessons learned from TARGET[i] series development, other ASICs

IRSX design review (September – if ready)

#### **Example: linearity improvement**

#### Expectations – matched to measurements

- Noise/amplitude

- Non-linearity

- Timebase non-uniformity

1GHz analog bandwidth, 5GSa/s

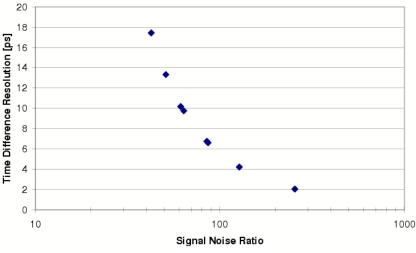

Time Difference Dependence on Signal-Noise Ratio (SNR)

G. Varner and L. Ruckman NIM A**602 (2009) 438-445**. Simulation includes MCP response

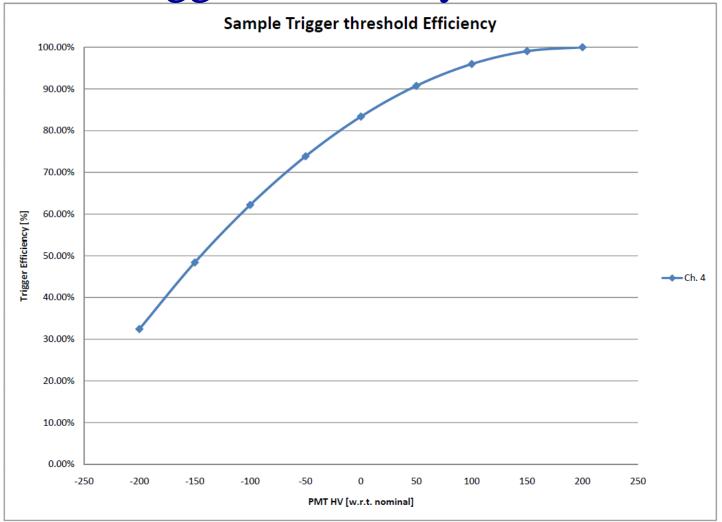

#### **Trigger Efficiency estimate**

Simple estimate based upon trigger threshold dependence

### Use as cross-check for detailed fit estimate, though robust (insensitive to laser coupling/optical fiber alignment)